12月7日,比利時微電子研究中心(imec)通過官網宣布,在近日的2024年IEEE 國際電子器件會議 (IEDM)上,其展示了一種基于 CFET 的新標準單元架構,其中包含兩排 CFET,中間有一個共享的信號路由墻。

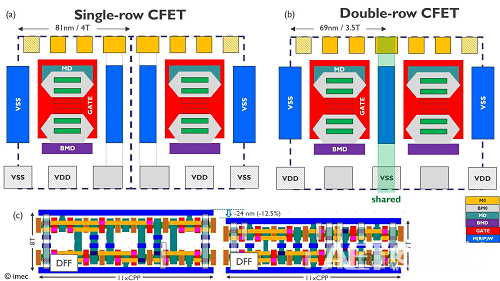

根據 imec 的設計技術協同優化 (DTCO) 研究,這種雙排 CFET 架構的主要優點是簡化了流程,并顯著減少了邏輯和 SRAM 單元面積。與傳統的單排 CFET 相比,新架構允許標準電池高度從 4T 降低到 3.5T。

半導體行業在制造(單片)CFET 器件方面取得了長足的進步,這些器件有望在邏輯技術路線圖中取代全環繞柵極納米片 (NSH)。當與用于供電和信號路由的背面技術相結合時,nFET 和 pFET 器件的堆疊有望在功率、性能和面積 (PPA) 方面帶來優勢。

然而,在電路層面,仍有幾種選擇可以將 CFET 集成到標準單元中,以維持或增強預期的 PPA 優勢。特別具有挑戰性的是中間線路 (MOL) 連接,即將源極/漏極和柵極觸點連接到第一條金屬線(背面和正面)并確保電源和信號從上到下的連接的互連。

通過比較標準單元架構的 DTCO 研究,imec 表明,雙排 CFET 為 A7(7埃米,即0.7nm)邏輯節點提供了可制造性和面積效率之間的最佳權衡。這種新架構從基本單元開始,其中 CFET 的一側針對電源連接進行了優化,包括將電源從背面輸送到頂部設備的電源軌 (VSS) 和底部設備的直接背面連接。另一側通過提供中間布線墻 (MRW) 來實現從上到下的連接,從而針對信號連接進行了優化。然后,通過鏡像兩個基本單元(具有兩排堆疊器件)形成雙排 CFET 標準單元,這兩個基本單元共享相同的 MRW 以進行信號連接(參見圖 1)。

△圖1-(a)單行CFET 和(b)雙行CFET的概念表示。觸發器(D型觸發器或DFF)的布局顯示,當從單行過渡到雙行CFET時,單元高度和面積減少了24nm (或12.5%)

imec DTCO 項目總監 Geert Hellings 表示:“我們的 DTCO 研究表明,每 3.7 FET 有一個共享 MRW 就足以構建邏輯和 SRAM 單元。與“經典”單排 CFET 相比,這使我們能夠進一步將標準電池高度從 4 T 降低到 3.5T。這意味著 SRAM 單元的面積顯著減少了 15%。與采用 A14 NSH 技術構建的 SRAM 相比,基于雙排 CFET 的 SRAM 可實現超過 40% 的面積收縮,為 SRAM 提供了進一步的擴展路徑。雙排 CFET 還簡化了工藝,因為兩排 CFET 器件之間共享 MRW 溝槽。這樣就無需額外的高縱橫比過孔來連接頂部和底部器件(如有必要),從而降低了 MOL 處理的復雜性和成本。

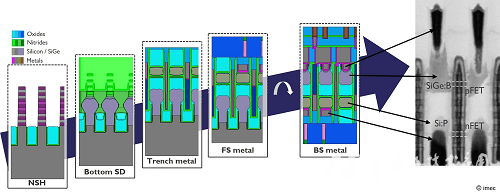

“自 7nm 技術節點以來,除了傳統的器件擴展外,通過 DTCO 進行的標準單元優化在節點到節點密度增加中提供了越來越大的份額,”Geert Hellings 補充道。“對于我們對 CFET 架構的 DTCO 研究,我們從未來 CFET 晶圓廠設想的工藝能力開始,以確保與行業相關的工藝流程(圖 2)。此外,我們還通過在 imec 的 300 毫米潔凈室中進行的技術概念驗證來驗證我們的虛擬晶圓廠概念。虛擬晶圓廠和真實試產線活動的結合是推進我們路線圖的關鍵一步。”

△圖2-用于構建雙排CFET架構的虛擬流程。使用3D Coventor模擬的工藝流程從“虛擬"CFET晶圓廠的規格開始,預測未來的加工能力和設計裕度。放大圖像代表了在imec的300毫米研發潔凈室設施內制造的單片CFET技術演示器的TEM。

因此,同樣在 IEDM 上,imec 實驗展示了這種雙排 CFET 架構的一個關鍵構建塊:一個功能性單片 CFET,其背面直接接觸底部 pMOS 器件的源極/漏極。這是通過 EUV 背面圖案化實現的,該圖案確保了密集的背面電源和信號布線,以及從正面創建的源極/漏極、背面接觸和隨后的背面金屬層之間的緊密覆蓋(<3nm 精度)(圖 2)。