摩爾定律不僅僅是關于晶體管數量的簡單經驗法則,它還是一種經濟、技術和發展的力量——而且強大到足以推動一些最大的芯片制造商采用面向未來的架構方法。

這種力量促使 AMD 的一些主要架構師通過采用chiplet(小芯片)方法,圍繞曾經預期的新技術開發節奏重新規劃路線。

我們稍后會詳細了解他們考慮的原因和考慮的內容,但首先,奠定基礎很有用。

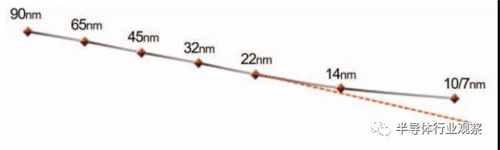

AMD公布了自己的內部估計(右),并對過去十年多出現的重要新工藝節點的粗略日期進行了估算。請注意 14nm 發生的情況——新技術以兩年為周期的頻率不斷發展,但隨著這一跳躍,它移動到三年并繼續擴展。該圖表充分說明了我們已經非常了解的內容——摩爾定律正在下滑,很快,這種下滑將是急劇的。

“制造集成芯片的成本一直在穩步攀升,由于增加了掩模層(例如用于多重圖案化)、更具挑戰性和更復雜的制造(先進冶金、新材料)等,最新一代芯片的成本急劇增加,” AMD 團隊解釋。“處理器制造商不僅要為每個新的工藝節點等待更長時間,而且當技術可用時,他們還必須支付更多費用。”

成本壓力很明顯:在這一點上瞄準更高的密度將減緩創新,正如 AMD 團隊指出的那樣,盡管高密度設備的最終價格可以抵消一些高成本,“該行業現在正面臨著光刻掩模版的限制,這是可以制造多大硅芯片的實際上限。”

“每個小芯片都是使用與單片情況相同的標準光刻程序制造的,以生產更多數量的較小小芯片。然后單個小芯片進行 KGD 測試。現在,對于與單片情況相同的故障分布,每個潛在缺陷導致僅丟棄大約四分之一的硅量。小芯片可以單獨測試,然后重新組裝并封裝到完整的最終 SoC 中。總體結果是,每個晶圓都可以產生數量明顯更多的功能性 SoC。”

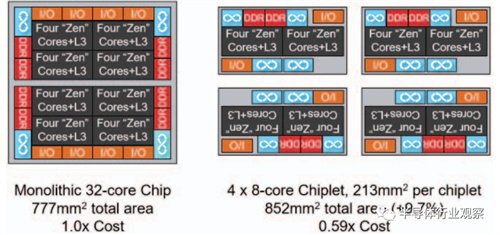

上面的示意圖顯示了一個假設的單片 32 核處理器。AMD 表示,他們自己的內部分析和產品規劃練習表明,這樣的處理器在 14 納米工藝中需要 777 平方毫米的芯片面積。“雖然仍處于光罩限制范圍內,因此在技術上可制造,但如此大的芯片將非常昂貴,并使產品處于潛在的缺乏競爭力的位置。”

大部分讀者已經很清楚這些趨勢,但值得強調,因為這些壓力是 AMD 廣泛的小芯片戰略的核心。盡管這種方法的成本很高,但這就是全部。畢竟,如果小芯片是一個明顯的贏家,整個行業早就會追逐它了。

“小芯片設計需要更多的工程工作來將 SoC 劃分為正確數量和類型的小芯片。存在多種可能性,但并非所有可能性都能滿足成本限制、性能要求、IP 和芯片重用的簡易性等,”AMD 團隊解釋道。它還需要對互連進行重大研發,涉及更長的路線,可能具有更高的阻抗、更低的可用帶寬、更高的功耗和/或更高的延遲。隨著電壓、時序、協議、SerDes 的變化,以及能夠在更多元素上復制所有測試和調試,互連的復雜性變得更加雜草叢生——所有這些都使小芯片看起來不那么明顯。

盡管存在這些復雜性,但小芯片方法的大部分優勢在基于四個復制小芯片的第一代 AMD EPYC 處理器中變得明顯。其中每個都有 8 個“Zen”CPU 內核,帶有 2 個 DDR4 內存通道和 32 個 PCIe 通道,以滿足性能目標。AMD 不得不為四個小芯片之間的 Infinity Fabric 互連留出一些額外的空間。設計團隊討論了從第一次運行中吸取的成本教訓:

“在 14 納米工藝中,每個小芯片的芯片面積為 213 平方毫米,總芯片面積為 4*213 平方毫米 = 852 平方毫米。與假設的單片 32 核芯片相比,這意味著大約 10% 的裸片面積開銷。基于使用成熟工藝技術的歷史缺陷密度數據的 AMD 內部良率建模,我們估計四小芯片設計的最終成本僅為單片方法的約 0.59,盡管總硅消耗量增加了約 10%。”

除了降低成本之外,他們還能夠在產品中重復使用相同的方法,包括使用它們構建一個 16 核部件,使 DDR4 通道增加一倍并提供 128 個 PCIe 通道。

但這一切都不是免費的。當小芯片通過 Infinity Fabric 進行通信時會引入延遲,并且由于同一小芯片上的 DDR4 內存通道數量不匹配,因此必須謹慎處理某些內存請求。

這些教訓被用于第二代 7nm Epyc 處理器。有關于各種權衡和技術挑戰的令人難以置信的豐富的討論,以及成本和性能。包括封裝決策背后的因素,共同設計挑戰,優化和類似的方法的跨產品的擴展。

“除了技術挑戰之外,在如此多的細分市場中實施如此廣泛的小芯片方法還需要技術團隊、業務部門和我們的外部合作伙伴之間的大量合作和信任,”該團隊總結道。

“跨市場的產品路線圖必須仔細協調并相互安排,以確保在合適的時間推出合適的芯片以推出每種產品。意外的挑戰和障礙可能會出現,世界一流且充滿激情的 AMD 工程團隊遍布全球。AMD 小芯片方法的成功既是工程上的壯舉,也是對擁有不同技能和專業知識的團隊的力量的證明,他們為實現共同的目標和共同愿景而共同努力。”