三星代工廠對其使用全環柵 (GAA) 晶體管或三星稱之為多橋溝道場效應晶體管 (MBCFET) 的3納米級工藝技術的計劃進行了一些更改。根據三星直接提供的新信息,它的第一個3nm版本3GAE(3nm gate-all-around early)似乎比預期晚了一年進入量產,但它似乎已經取消了這項技術來自其公共路線圖,表明它可能僅供內部使用。

同時,3GAE的繼任者3GAP(3nm gate-all-around plus)節點仍在路線圖中,有望在2023年實現量產。

2022年3GAE步入正軌,但不適合所有應用

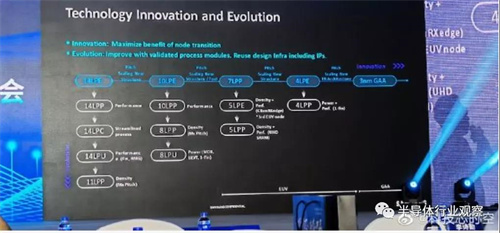

在最近在中國舉行的 2021 代工論壇上,三星代工展示了其更新的公共技術路線圖。

在其 FinFET 技術方面,5LPP 和 4LPP 節點都是路線圖的新節點,并分別在 2021 年和 2022 年進行大批量制造 (HVM)。

對于 GAA 技術,路線圖中沒有 3GAE,但有 3GAP。我們聯系了三星,一位代表確認 3GAE 技術仍處于 2022 年量產的軌道上。從幻燈片中,我們可以看到基于 MBCFET 的 3GAP 將在 2023 年的某個時候進入其 HVM 階段。

發言人表示:“至于3GAE工藝,我們一直在與客戶討論,預計2022年量產3GAE。”

(圖片來源:科技芯時空)

公共路線圖中沒有 3GAE 流程可能是因為它僅適用于三星自己的 LSI 部門,就像其他一些 (E)arly 節點一樣。話雖如此,該公司演示的幻燈片中仍提到了上一代 (E) arly 節點。

三星最初 于 2019 年 5 月宣布了其基于 MBCFET 的 3GAE 和 3GAP 節點。當時,該公司承諾與 7LPP 相比,3GAE 的性能提高35%,功耗降低50%,面積減少45%。此外,該公司宣布了其3nm PDK v0.1的可用性,當時表示將在 2021 年底開始使用 3GAE 進行批量生產。根據最新信息,隨著 2022 年的到來,人們可能會將其解釋為基于大規模啟用 GAA 設計的延遲或錯誤計算。

然而,從好的方面來說,三星 幾周前流片了 第一個 3 nm 測試芯片。它還宣布推出與新制造技術兼容的 Synopsys EDA 工具。使用依賴全新晶體管的制造工藝始終是一個挑戰——除了新的電子設計自動化 (EDA) 工具外,芯片開發商還需要全新的 IP。我們期待聽到更多關于這方面的披露。

FinFET上的新4LPP節點

雖然看起來普通客戶要到2023年才會使用三星的3 nm節點,但新發布的4LPP 將在2022年滿足該公司客戶的要求。由于4LPP依賴于熟悉的FinFET,因此對三星的客戶來說會容易得多與生命周期早期的任何3nm GAA節點相比,使用此節點。

(圖片來源:科技芯時空)

值得注意的是,三星現在將其5納米和4納米級技術視為其幻燈片上的不同節點分支。此前,該代工廠將其 4LPE 視為其 7LPP 工藝的演變。或許這是因為4納米將提供比5納米更明顯的PPAc(功率、性能、面積、成本)優勢,或者因為存在實質性的內部變化(例如,新材料、極紫外光刻的顯著增加使用等)。

例如,三星的一張幻燈片特別提到了 5LPE 和 5LPP 的密度和性能改進,但只提到了 4LPP 的功耗和性能改進。如果其中一個節點不滿足某些期望,重疊技術也將有助于降低風險。

(圖片來源:科技芯時空)

令人驚訝的是,三星代工廠將在 2021 年左右同時使用其 4LPE 和 5LPP 技術提高產量,這可能使其能夠為不同的芯片設計提供不同的 PPAc 優勢。

總結

雖然三星代工廠的 GAAFET/MBCFET 3 nm計劃似乎已經改變并推遲了一年,但這對公司來說不太可能是一個大問題,因為其 (E)arly 節點從未被廣泛采用。為了覆蓋這額外的一年,該公司新的基于5LPP和4LPP FinFET的技術將為三星代工廠的客戶提供PPA優勢,并使該公司在將EUV設備用于其 3GAE/3GAP 節點之前獲得更多的經驗。