近年來隨著全球芯片和軟件產業規模的不斷擴大,以及芯片技術的更新升級,對電子設計自動化(EDA)的需求越來越大。EDA是集成電路設計必需、也是最重要的軟件工具,具有“芯片之母”的美稱。

作為集成電路產業鏈最上游、最高端的環節,EDA撬動的是全球16500億元美金的電子產品市場。縱覽整個EDA市場,因其技術的高門檻,集中度很高,三大巨頭占據90%市場份額。但在數字經濟時代的巨大市場需求和新興技術的蓬勃發展的驅動下,三巨頭的堡壘漸漸開始松動,我國也誕生了一批優秀的本土EDA企業。

在這批本土企業中,芯華章科技股份有限公司(以下簡稱“芯華章”)作為一家今年3月份才成立的“后浪”,因為初創團隊皆為行業里的具備多年經驗、備受信賴的精英,并快速聚集了EDA公司發展最關鍵的人才、技術、資金、市場等要素,吸引了眾多的關注與青睞。這個團隊在成立之初,就將目光聚焦在了國內EDA領域的短板——數字驗證EDA。

兩大新品強勢出擊

EDA主要包含“模擬芯片、數字芯片驗證和數字芯片實現”三大部分。從國內看,盡管近年來國產EDA在模擬芯片工具上取得了一定進展,但在數字仿真、驗證等多個環節仍存在多處短板,對國外的依賴大,產業鏈脆弱。

芯華章涉及的業務場景是EDA技術密度最高、需求量最大的芯片驗證環節。創始人兼董事長王禮賓表示,公司的目標是突破現有技術壁壘,開發出全流程EDA驗證工具與系統,推出包含硬件仿真器、FPGA原型驗證、形式驗證、智能驗證、邏輯仿真等產品與平臺。

11月26日,芯華章正式發布高性能多功能可編程適配解決方案“靈動”(EpicElf),以及國內率先支持國產計算機架構的全新仿真技術。

“靈動”是為了解決行業痛點而誕生的,主要用于FPGA原型化平臺,可一卡替代多種原型驗證進口子板,具備強大的功能和適配能力,可進一步加快驗證收斂,助力軟硬件協同開發,提高芯片設計的研發效率。

在集成電路(IC)開發過程中,驗證是非常昂貴的流程,尤其是數字芯片驗證部分,其占據了芯片設計過半的研發時間與成本。目前,芯片已經進入系統級(System on Chip, SoC)時代,數百億顆晶體管和數公里長的連線集成在芯片上,高度的復雜性意味著驗證環節困難重重,如果驗證工作不完備,將導致上億美金級的資金和時間付諸流水,與市場機遇錯身而過等不可逆的結果。

根據芯華章硬件驗證平臺研發副總裁陳蘭兵介紹,傳統或自研接口子板采用傳統架構,在一定程度上增加了方案的復雜度,使開發人員需要投入大量的調研時間。同時成本高,存在交貨期風險。并且只有單一功能,不可編程。

對比傳統或自研接口子板,“靈動”具備以下優勢:

首先是全新的硬件架構體系,“靈動”可以支持多種不同高速接口協議,釋放原型化的IO資源并提高原型化的邏輯利用率。

來源:芯華章

其次是成本優勢,“靈動”最多可節約四倍的使用成本,并且能夠同時支持多種接口協議。

“靈動”還具備兩種使用模式,可直接使用,也可完全由用戶做自定義編程,提高了使用的靈活性。

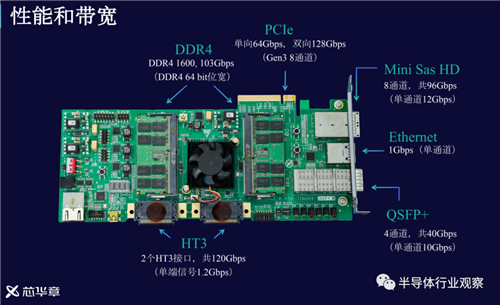

最后是強大的高速系統互連設計能力,“靈動”能夠實現1.2Gbps 單線高速傳輸,發揮芯片最大的吞吐能力。

來源:芯華章

同時發布的另一重磅新品,是芯華章的全新仿真技術。這同樣也是市場上首個支持國產計算機架構的動態仿真技術,不僅兼容現有國際和國內的計算機架構,更能面向未來,有助于支持新一代的多核與異構等計算機架構。

仿真技術是保證集成電路設計正確性的關鍵技術之一,芯片設計公司通過軟件仿真數字電路的行為,發現并修復問題。然而,目前主流的仿真技術僅支持x86架構。而未來還有多核與異構等計算機架構,主流僅支持x86架構的仿真技術在不具備拓展性的同時,更無法滿足高效處理的市場需求。

芯華章動態仿真及形式驗證研發副總裁齊正華介紹道,芯華章的仿真技術基于LLVM的全新架構,突破傳統仿真器僅支持單一x86架構的局限,具備靈活的可移植性,可兼容當前主流架構并有助于支持未來多核與異構的大規模計算機處理器結構。

具體看來,與傳統仿真技術相比,芯華章全新仿真技術具備以下優勢:

1、全新的架構體系:靈活的可移植性、友好的軟硬件生態支持;

2、有助于支持不同的處理器計算架構,如x86, Arm, RISC-V, MIPS, GPGPU, NPU等;

3、全新的數據結構和優化的算法:通過算法,優化驗證算力分配,進一步提高芯片設計驗證效率;

4、符合IEEE1800 標準;

5、事件驅動型,精度與目前商用數字仿真器一致;

6、基于LLVM的原生編譯后端。

在諸多優勢下,芯華章全新仿真技術比主流仿真技術善用更多的計算算力,并能進一步提高芯片設計驗證效率。

來源:芯華章

芯華章此次發布的驗證EDA產品與技術,已經在國產飛騰服務器上通過了驗證,能兼容當前的產業生態,并面向未來有助于支持下一代計算機架構,是建設中國自主研發集成電路產業生態的重要里程碑。

天津飛騰信息技術有限公司副總經理郭御風指出,“飛騰的核心研發集中在芯片的設計和創新,而EDA驗證在芯片的研發過程起著非常關鍵的作用,是核心環節的關鍵技術。芯華章在驗證領域有深入的理解和多年的研發經驗,基于處理器芯片的架構和需求,快速研發出了適合國產CPU架構的驗證技術解決方案,這是極具開創性的重要里程碑,不僅能為我們的驗證工作帶來更多的便利,更能給芯片設計公司提供更多的選擇。”

雄厚的技術積累是底氣

在談到芯華章時,我們會提到率先支持國產計算機架構的動態仿真技術,也會提到中國首個開源EDA技術社區,全球最快的開源數字仿真器EpicSim等。自成立以來的短短8個月內,這家EDA“后浪”給了我們太多驚喜,很大程度上與這家公司擁有雄厚的技術家底有關系。

從王禮賓的介紹中我們得知,芯華章是一家“高起點、厚積累、重人才”新型EDA公司,匯聚了來自國際領先EDA、集成電路設計、軟件以及人工智能企業,在各自領域工作超過15年,擁有豐富的產品研發經驗的研發人才。不僅如此,芯華章還在8月份延攬到林財欽(TC Lin)出任首席科學家后,陸續獲得了全球頂尖技術人才如EDA和AI算法專家林揚淳(YT Lin)、系統設計專家顏體儼博士的認可和加盟。

在此基礎上, 芯華章研發團隊將基于過去多年的EDA研發經驗和技術積累,在當前最先進的軟件工程方法學及高性能硬件架構的基礎上,充分融合云計算、AI等新一代技術,通過新路徑對EDA進行研發,打造了全流程驗證產品與系統。

在融合前沿技術打造面向未來的新一代EDA工具的同時,芯華章在今年8月就宣布啟動開源EDA生態項目,并在9月上線了中國首個開源EDA技術社區——EDAGit.com。在此社區中,其技術團隊基于經典驗證方法學與技術,陸續推出商用級別的開源EDA驗證產品,開源加速創新已經是經過不同領域驗證過的有效途徑,芯華章希望能借由開放、共創的形式,能夠降低EDA使用門檻,發現并培養更多對EDA技術感興趣的優秀人才,充分釋放創新活力。

據了解,公司已推出的EpicSim是當前全球最快的開源數字仿真器。而第二款開源EDA產品“靈驗”(EpicFV),更是全球首款開源形式驗證工具。“靈驗”在用戶輸入RTL設計和SystemVerilog斷言描述設計規范的情況下,可以自動進行語法解析、設計綜合、斷言解析,并且基于分布式計算理論自動調度引擎求解斷言,加速驗證收斂,從而降低形式驗證工具的使用門檻。

王禮賓表示,截止11月中旬,已經有400多個專業人士參與使用芯華章的開源工具并持續在社區中進行交流,獲得不小的收獲。與此同時,芯華章也在其中發現了不少EDA人才,并將加大對開源社區的投入,培育EDA人才成長的良好環境。

不僅如此,芯華章還力邀國內外有豐富發經驗的EDA專家、學者、教授,共同打造“X-行動”,合作定制面向新生代工程師的EDA培訓課程體系,并通過甄選優質生態項目實現技術攻堅,同時設立項目創新激勵計劃、專利申請激勵計劃等,積極為芯華章企業自身以及中國EDA行業儲備優秀的新生代技術力量。

“后浪”芯華章將繼續融合我國AI、云計算和大數據優勢技術給予的技術高起點,打造出面向未來的新一代EDA軟件和系統。芯華章沒有技術包袱,可以快速融合前沿技術,通過全新路徑對EDA 進行研發,這一點,是傳統EDA巨頭無法與之匹敵的。

總 結

當下,芯片需求量隨著數字經濟時代的到來而激增,2025年集成電路行業總產值保守估計將超過2萬億元。因此,國內EDA市場有著極大的發展空間。

國內有如芯華章等不少EDA廠商正在各自的領域中奮力前進,他們或專注于模擬芯片、或專注于數字前端又或者是數字后端,相信在不久的將來,他們就能利用在各自領域的突破形成合力,為中國芯片產業鏈補齊EDA短板。