前言

電子技術的飛速發展,尤其是消費類電子產品在成本、產品功能及品質的更高要求,使消費類電子產品的設計不是簡單地要求設計出來,而是要考慮低成本高品質。 CPLD的成本低,占用PCB面積小,功耗低和靈活的后期可編程特性在嵌入式設計中得到越來越廣泛的應用。

由于CPLD資源較小,大部分工程師都用CPLD來實現整合邏輯電路,擴展主處理器的I/O功能,或做電源管理功能,由于CPLD內部沒有振蕩器,而振蕩器的功能對于CPLD做電源管理,產品的系統管理尤為重要,如果在CPLD外部加一個振蕩器就增加了整個設計的成本。利用CPLD內部的反向器,再加上外部簡單的RC,即可以實現一個簡單的振蕩器供CPLD內部設計使用,可以降低設計成本,靈活性強,穩定性高。

CPLD內部施密特觸發器

CPLD內部施密特觸發器電器特性見表1。目前大部分使用的CPLD都需要兩個電源VCC和VCCIO,VCC就是CPLD內部的核電壓,VCCIO是CPLD所有I/O 引腳電壓。

從表1看出,VT+和VT-是取決于VCCIO的電壓。目前大部分設計都選用VCCIO為3.3V,所以,VT+ (min.) = 0.5 × 3.3V = 1.65V,VT+ (max.) = 0.8× 3.3V = 2.64V

VT- (min.) = 0.2 × 3.3V = 0.66V VT-(max.) = 0.5 × 3.3V = 1.65V

從上面給出的VCCIO 為3.3V計算可以看出,對于施密特觸發器當輸入電壓在1.65V下輸出都為低電平,當輸入電壓在1.65V之上都為高電平,1.65V為高低電平的臨界點。

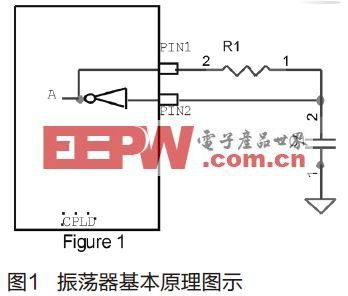

振蕩器實現

利用CPLD內部的施密特觸發器使輸入波形得到校正,再加上反向器反向和外部RC實現振蕩器,只需要在使用CPLD的任意兩個I/O PIN引腳(當然從CPLD內部原理來看最好是使用相鄰的兩個PIN引腳,會減小CPLD內部資源的占用)。其中一個PIN 引腳串入電阻,外接一個對地電容,當內部的A點為高電平時,PIN1會通過R1對C1充電,由于電容的電壓不可越變,電壓是對電流的積分,所以電壓會逐漸上升,當電平上升至0.5 × VCCIO,CPLD施密特觸發器才認為是高電平,再經過內部的反向器會反向,所以A 點會變成低電平,這時C1 會通過R1逐漸放電,當放電電平低于0.5 x VCCIO時,反向器反向A點又變回高電平,這樣反復的振蕩就構成了一個穩定的振蕩器時鐘源(見表1)。

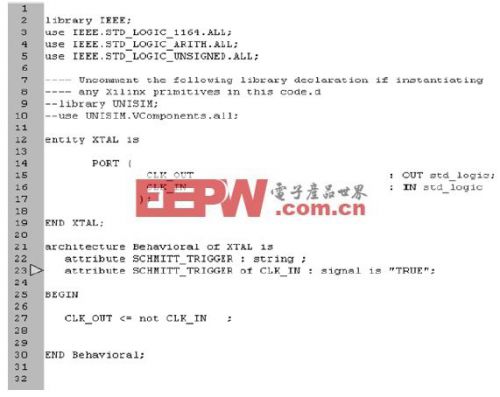

CPLD實現代碼

本設計使用VHDL語言,選用XILINX 公司的COOLRUNNER-II系列的CPLD器件, 基于0.18nm CMOS CPLD, 3.8ns PIN-to-PIN延時,快速JTAG下載,2個bank,具體實現見代碼列表。

振蕩器應用

上述代碼通過XILINX的編譯綜合器后,會產生一個可下載檔案,此檔案可以通過JTAG直接下載到芯片中使用,由于代碼示例的為一個實時振蕩器,也就是只有芯片上電,振蕩器部分會一直工作,對于用于電源管理的嵌入式產品設計,由于一直振蕩帶來額外的電功耗損耗,功耗的損耗和振蕩的頻率是相關的,當頻率越高時,功耗越大。所以,設計還可以再被優化使用。比如,當符合什么條件時振蕩器才開始振蕩,或者達到什么條件時振蕩器停止振蕩,這樣靈活的優化設計會給產品帶來更多的附加價值,延長電池的使用壽命。

振蕩器的振蕩頻率是通過外部引腳的電阻和電容來調整的,當電阻越小,電容越小時,振蕩的頻率就很高。當電阻很大時,電容也變大,振蕩的頻率就會變低。振蕩器的精度取決于外面電阻和電容的精度,電阻的精度以現在工藝可以做到1%的正負誤差,電容可以選擇5%的正負誤差,高精度的電阻和電容會帶來比較精準的振蕩頻率。

結語

本文的設計充分利用了CPLD內部的硬件資源和VHDL靈活嚴謹的編程和外加簡單的RC實現了一個振蕩時鐘源,既可供CPLD內部設計使用,也可以供給外部其他設計使用,該設計減小了設計的復雜性,通過CPLD的靈活可編程性降低了產品的成本,具有一定的商業應用價值。