引 言

嵌入式DDR(Double Data Rate,雙數據速率)設計是含DDR的嵌入式硬件設計中最重要和最核心的部分。隨著嵌入式系統的處理能力越來越強大,實現的功能越來越多,系統的工作頻率越來越高,DDR的工作頻率也逐漸從最低的133 MHz提高到200 MHz,從而實現了更大的系統帶寬和更好的性能。然而,更高的工作頻率同時也對系統的穩定性提出了更高的要求,這需要硬件設計者對電路的布局走線有更多的約束和考慮。而影響整個系統能否工作正常且穩定的最重要的部分就是DDR部分的電路設計。

嵌入式系統使用DDR內存,可以在傳統的單數據數率內存芯片上實現更好的性能。DDR允許在不增加時鐘頻率和數據位寬的條件下,一個時鐘周期內能夠處理兩個操作。增加的數據總線性能是由于源同步數據選通允許數據同時在選通脈沖的上升沿和下降沿被獲取。

DDR雖然能夠給嵌入式設計帶來更好的性能,但是設計者必須比以往的SDR設計更小心地處理DDR部分的PCB布線部分,否則不僅不能實現好的性能,整個嵌人式系統的穩定性也會受到影響。DDR比傳統的SDR有更短的信號建立保持時間、更干凈的參考電壓、更緊密的走線匹配和新的I/O口信號,并且需要合適的終端電阻匹配。這些都是要面對的新的挑戰。

1 DDR總線結構

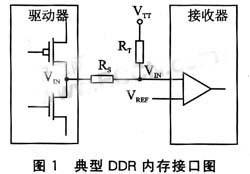

對于DDR內存,JEDEC建立和采用了一個低壓高速信號標準。這個標準稱為“短截線串聯終結邏輯(StubSeries Terminated Logic,SSTL)”。SSTL能夠改進數據通過總線傳輸的信號完整性,這種終端設計的目的是防止在高速傳輸下由于信號反射導致的數據錯誤。

在一個典型的內存拓撲結構中,如果使用了串聯匹配電阻(RS),那么它應該放在遠離DDR控制器的位置。這種方法能夠節約控制器附近寶貴的電路板空間,避免布線擁塞和繁瑣的引腳扇出;而且也優化了從控制器到內存芯片的信號完整性,在這些位置往往有很多地址和命令信號需要可靠地被多個內存接收。

最普通的SSTL終端模型是一種較好的單終端和并聯終端方案,如圖1所示。這種方案包含使用一個串聯終端電阻(Rs)從控制器到內存,以及一個并聯終端電阻(RT)上拉到終端電壓(VTT)。這種方法常見于商用電腦的主板上,但目前的嵌入式主板上為了獲得更好的信號完整性和系統穩定性,也常常使用。RS和RT的值是信賴于具體的系統的,應該由板級仿真確定具體的值。

2.3 信號組布線順序

為了確保DDR接口最優化,DDR的布線應該按照如下的順序進行:功率、電阻網絡中的pin腳交換、數據信號線布線、地址/命令信號布線、控制信號布線、時鐘信號布線、反饋信號布線。

數據信號組的布線優先級是所有信號組中最高的,因為它工作在2倍時鐘頻率下,它的信號完整性要求是最高的。另外,數據信號組是所有這些信號組中占最大部分內存總線位寬的部分,也是最主要的走線長度匹配有要求的信號組。

地址、命令、控制和數據信號組都與時鐘的走線有關。因此,系統中有效的時鐘走線長度應該滿足多種關系。設計者應該建立系統時序的綜合考慮,以確保所有這些關系都能夠被滿足。

2.4 各組信號布線長度匹配

時鐘信號:以地平面為參考,給整個時鐘回路的走線提供一個完整的地平面,給回路電流提供一個低阻抗的路徑。由于是差分時鐘信號,在走線前應預先設計好線寬線距,計算好差分阻抗,再按照這種約束來進行布線。所有的DDR差分時鐘信號都必須在關鍵平面上走線,盡量避免層到層的轉換。線寬和差分間距需要參考DDR控制器的實施細則,信號線的單線阻抗應控制在50~60 Ω,差分阻抗控制在100~120 Ω。時鐘信號到其他信號應保持在20 mil*以上的距離來防止對其他信號的干擾。蛇形走線的間距不應小于20 mil。串聯終端電阻RS值在15~33Ω,可選的并聯終端電阻RT值在25~68 Ω,具體設定的阻值還是應該依據信號完整性仿真的結果。

數據信號組:以地平面為參考,給信號回路提供完整的地平面。特征阻抗控制在50~60 Ω。線寬要求參考實施細則。與其他非DDR信號間距至少隔離20 mil。長度匹配按字節通道為單位進行設置,每字節通道內數據信號DQ、數據選通DQS和數據屏蔽信號DM長度差應控制在±25 mil內(非常重要),不同字節通道的信號長度差應控制在1 000 mil內。與相匹配的DM和DQS串聯匹配電阻RS值為0~33 Ω,并聯匹配終端電阻RT值為25~68Ω。如果使用電阻排的方式匹配,則數據電阻排內不應有其他DDR信號。

地址和命令信號組:保持完整的地和電源平面。特征阻抗控制在50~60 Ω。信號線寬參考具體設計實施細則。信號組與其他非DDR信號間距至少保持在20 mil以上。組內信號應該與DDR時鐘線長度匹配,差距至少控制在25 mil內。串聯匹配電阻RS值為O~33 Ω,并聯匹配電阻RT值應該在25~68 Ω。本組內的信號不要和數據信號組在同一個電阻排內。

控制信號組:控制信號組的信號最少,只有時鐘使能和片選兩種信號。仍需要有一個完整的地平面和電源平面作參考。串聯匹配電阻RS值為O~33 Ω,并聯匹配終端電阻RT值為25~68 Ω。為了防止串擾,本組內信號同樣也不能和數據信號在同一個電阻排內。

2.5 電源部分的設計分析

通常情況下,DDR供電電壓是2.3~2.7 V,典型值是2.5 V,工作頻率的不同可能引起正常工作電壓的不同。參考電壓VREF是1.13~1.38 V,典型值是1.25 V。VTT以VREF為參考,電壓范圍是(VREF-0.4 V)-(VREF+0.4 V)。由于VREF只是給差分接收器端提供一個直流參考電平,所以電流比較小,最大只有3 mA。VTT的電流由于上拉的緣故,在輸出端輸出高電平時,VTT應能流入電流;在輸出端輸出低電平時VTT電流輸出。故VTT必須能同時有流入和流出電流,電流的大小依賴于總線上同時出現的電位狀態,從常用的設計來看最大可以從2.3 A到3.2 A。

由于VREF電壓作為其他信號接收端的重要參考,故它的布線設計也是十分重要的。疊加在VREF電壓的串擾或噪聲能直接導致內存總線發生潛在的時序錯誤、抖動和漂移。很多電源芯片會把VREF和VTT從同一源輸出,但是由于使用的目的不同,走線也完全不同。VREF最好和VTT在不同平面,以免VTT產生的噪聲干擾VREF。而且無論是在DDR控制器端還是DDR存儲器端,VREF腳附近都應放置去耦電容,消除高頻噪聲。VREF的走線寬度應該越寬越好,最好為20~25 mil。

VTT電源應該單獨劃分一塊平面來供應電流,且最好放在DDR存儲器端。如果并聯終端匹配使用排阻的方式上拉,那么最好每個排阻都添加一個0.1 μF或0.01μF的去耦電容,這對于改善信號的完整性、提高DDR總線的穩定性都有很好的效果。

結 語

在帶有DDR的嵌入式系統主板中,設計PCB最難的部分莫過于DDR的走線設計。好的走線就等于有了好的信號完整性和好的時序匹配,總線在高速輸入/輸出數據過程中就不會出錯,甚至能夠有更好的抗串擾和EMC能力。DDR總線并行傳輸且速率較高,在設計過程中如果沒有按照嚴格的約束進行布線,在設備后期調試過程中,將會出現各種各樣異常問題,甚至是系統根本無法啟動。而這些問題在查找和調試中很難發現,以至于無法完成硬件的開發。最好的方法就是在設計時就充分考慮信號完整性和時序匹配的問題,在走線時就把這些規則運用進去;如果有條件,可以做一下仿真,預先驗證一下設計。這樣做出來的設計,系統的穩定性和可靠性才會更高。