1 引言

FIR數字濾波器能夠滿足濾波器對幅度和相位特性的嚴格要求,避免模擬濾波器的溫漂和噪聲等問題,具有精確的線性相位、易于硬件實現和系統穩定等優點,可廣泛應用于現代電子通信系統。實際信號處理應用往往要求系統兼具實時性和靈活性,而現有設計方案(如DSP)則難以同時達到這兩方面要求。而使用具有并行處理特性的FPGA實現FIR濾波器,具有很強的實時性和靈活性,因此為數字信號處理提供一種很好的解決方案。

在嵌入式導航計算機工程項目中,石英撓性加速度計的輸出信號需進行數字濾波才能為導航計算機提供原始數據,為此需要設計一款FIR數字濾波器。這里使用 MATLAB軟件和Altera公司的FPGA開發軟件QUARTUSⅡ進行FIR濾波器的設計仿真,該設計方案能夠直觀檢驗濾波器的設計效果,提高設計效率,縮短設計周期。

2 使用FIR IP Core設計濾波器

Altera公司提供的FIR Compiler是一個結合Altera FP-GA器件的FIR Filter Core,DSP Builder與FIR Compiler緊密結合。DSP Builder提供一個FIR Core的應用環境和仿真驗證環境。而FIR濾波器設計實質上是確定能滿足所要求的轉移序列或脈沖響應的常數問題,設計方法主要有窗函數法、頻率采樣法和等波紋最佳逼近法等,這里采用窗函數法。

2.1 濾波器指標設計

FIR濾波器設計需達到以下指標:低通濾波,采樣頻率Fs為1 000 Hz,截止頻率Fc為100 Hz,最小阻帶衰減As為50dB,16階濾波器,16位輸入數據寬度,14位系數數據寬度。

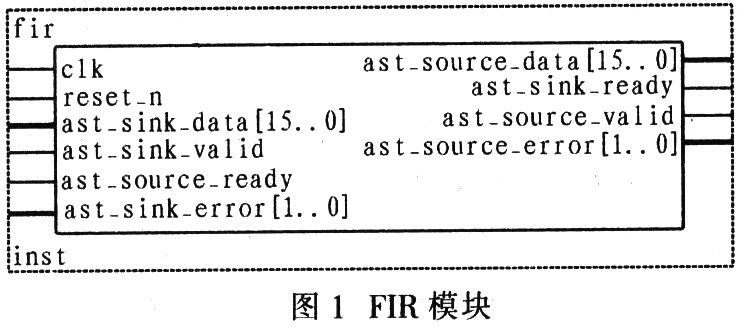

2.2 利用FIR IP Core生成FIR模塊

在FIR編譯器中,將FIR濾波器設置為16階低通濾波器,單速率采樣。采樣頻率為1 000 Hz,截止頻率為100 Hz,窗類型選擇海明窗,然后生成系數并保存。濾波器系數的計算以所能達到最高精度為目的,計算出的濾波器系數未考慮有限字長效應,必須量化濾波器系數。由于在FPGA內要使用硬件實現濾波器,因此采用定點計算。按照指標要求設置參數,生成的FIR模塊如圖1所示。

3 驗證方法的確定

基于FPGA的復雜DSP系統的調試驗證是一項繁瑣工作,采用傳統的邏輯分析方法調試基于FPGA器件實現的設計幾乎不可能。驗證方法決定驗證結果的準確性和驗證工作量的大小。目前對基于FPGA的FIR數字濾波器的驗證,通常采用輸入一個信號序列(白噪聲、多頻譜混合信號等)作為激勵,對濾波器的輸出結果進行分析對照,判斷濾波器是否符合設計要求。

4 利用Simulink檢驗濾波效果

Simulink是MATLAB中一個專門用于對動態系統進行建模、仿真和分析的軟件包。通過調用模塊,可以構成仿真數字濾波器特性的結構框圖。輸入低頻 50 Hz和高頻400 Hz的2個信號,利用所設計的濾波器進行濾波。建立仿真電路結構,導入前面所設計的FIR濾波器,如圖2所示。

圖3為輸入波形在Simulink中Scopel的波形,圖4為輸出波形在Simulink中Scope的波形。比較圖3和圖4可看出,該FIR濾波器可有效濾除高頻部分。因為在DSPbuilder中,輸入正弦波形是通過查找表得到的每個周期256個點的量化值形式,故無物理單位,因此輸出波形也是量化值形式。

5 使用ModelSim進行RTL級仿真

完成Simulink軟件中的模型設計,仿真成功后,需要在ModelSim中仿真。因為Simulink中的仿真屬于系統驗證性質,是對mdl文件進行算法級仿真,而生成VHDL描述是RTL級,針對具體硬件結構。二者之間可能存在軟件理解上的差異,轉換后的VHDL代碼實現可能與mdl模型描述的情況不完全相符,這就需要使用ModelSim進行RTL級功能仿真。圖5所示是采用ModelSim仿真的結果,即低通濾波器的輸出。可看出,與 simulink中的仿真結果基本一致。

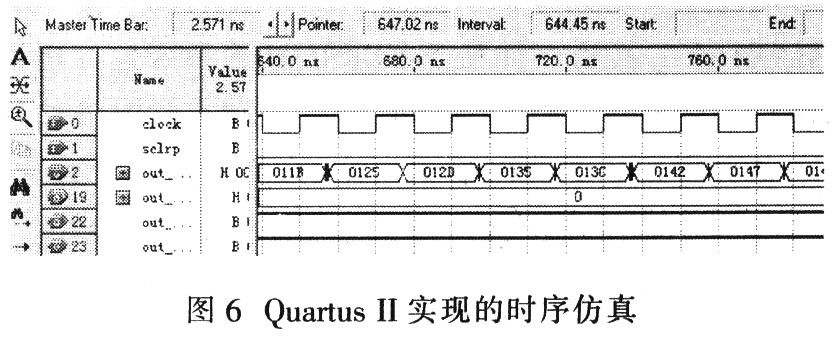

6 使用QUARTUS實現時序仿真

ModelSim完成的RTL級仿真只是功能仿真,其仿真結果并不能精確反映電路的全部硬件特性,因此,時序仿真仍十分重要。圖6是用QuartusⅡ實現的時序仿真,可看出,時序仿真滿足設計要求。

7 使用嵌入式邏輯分析儀SignalTap II測試

只進行工程軟件仿真遠遠不夠,還必須進行硬件仿真。signalTap II邏輯分析儀是Quartus II軟件中集成的一個內部邏輯分析軟件,使用它可以觀察設計的內部信號波形,方便用戶查找引起設計的缺陷。從Simulink建模仿真到Mod- elsim RTL仿真和Quartus II時序仿真,輸入正弦波都是仿真信號,而不是實際信號源。在硬件實際運行時,可以從外部信號源接入器件內部或者在其內部存儲正弦波數據。這里采用后者,即在頂層文件中引入LPM_ROM宏模塊,在其中存入正弦波數據的mif文件(存儲初始化文件),FIR濾波器模塊直接從ROM中讀取數據。實際測試發現,經過設計的低通濾波器后,高頻信號被濾除,只有輸出低頻信號(標準的正弦波),濾波效果滿足系統要求,嵌入式邏輯分析儀中的輸出波形如圖7所示。

8 結束語

本文在FPGA內利用DSPBuilder實現FIR數字低通濾波器,通過Simulink算法仿真和ModelSim進行RTL仿真,接著在 Quartus中進行時序仿真。最后用嵌入式邏輯分析儀SignalTapII進行實際測試,結果證明采用該方法設計的FIR數字低通濾波器功能正確,性能良好,可以提高FIR濾波器的設計質量,加快設計進程,驗證結果直觀明了。隨著各類數字信號處理的IP Cores的進一步完善,基于FPGA的DSP系統的應用會更加廣泛。