1.引言

可編程邏輯器件PLD(Programmable logic Device)就是由用戶進行編程實現所需邏輯功能的數字專用集成電路ASIC。可編程邏輯器件在現代電子工程設計中得到了廣泛應用。它是在PAL,GAL等邏輯器件的基礎上發展起來的,具有高密度,高速度,低功耗體系結構和邏輯單元,靈活以及運用范圍寬等特點,同時還具有設計周期短,制造成本低,開發工具先進,標準產品無需測試,質量穩定及可實時布線檢驗等優點。

現場總線技術廣泛應用于工業和軍用測控局域網中,它可以實現較遠距離、較快速度的信息傳輸,而且只需要雙絞線作為傳輸媒介,簡單可靠。但是,在該技術應用中總線控制器與微機之間的接口電路一般采用單片機來實現。采用這種方式將導致較長的研發周期和龐大的電路,且難于實現高速數據傳輸。本文利用CPLD成功地實現了嵌入式系統與CAN總線網絡的通信,速度快,易于實現,而且非常穩定。

本系統采用的器件是Altera公司的CPLD,屬于MAX7000系列。Altera公司的CPLD器件主要包括MAX系列、ACEX系列、FLEX系列和APEX系列。其中MAX系列器件為高速實

際應用提供了非常高的性價比,這基于它先進的MAX架構。MAX7000系列提供了速度最快的可編程邏輯器件解決方案,它基于CMOS EEPROM工藝,傳播延遲最小為3.5ns。

2.CPLD實現接口電路

實時控制系統中,測控局域網利用CAN控制器實現微機間的數據傳輸。其基本的設計思想是:由于PC總線協議與CAN控制器不一致,因而在它們中間設計了一個硬件電路作為接口來實現轉換。PC地址與數據總線是分離的,而CAN控制器數據與地址線通過分時復用來實現地址與數據分離,剛好與單片機一致。單片機技術雖然較成熟,但是,由于涉及單片機編程和開發的周期較長,且采用單片機系統需要較龐大的外圍電路,不利于研制系統應用于嵌入式系統中。因此,用可編程邏輯器件設計接口電路,可以有效解決這些問題。

本系統采用“主-從”式點對點通信。系統硬件由兩臺PC104主機和兩塊CAN總線通信模塊組成,如圖1所示。主機采用CPU主頻為300MHz的奔騰處理器;CAN總線控制器位SJA1000T;一帶屏蔽的雙絞線作為系統總線;通信波特率可用軟件設置為1Mbps;為了提高通信的可靠性,用CAN控制器的報文篩選器對報文進行篩選,來對由于干擾而產生的錯誤報文進行濾波。

圖1 系統硬件組成

本系統主要是利用主機PC(PC104)采集多個下位機從被控對象得到的數據,并進行實時控制和綜合調度,其原理框圖如圖2所示。

圖2 原理框圖

其中CPLD完成從CAN控制器到PC總線的數據轉換。CAN控制器負責從總線上采集數據。總線驅動部分由89C250完成總線驅動;光電隔離器完成CAN控制器與傳輸電纜的信號隔離,防止電纜上的非規則信號對CAN控制器產生干擾。

3.MAX+PLUSⅡ程序設計

Altera公司的MAX+PLUS Ⅱ是一個高效實用的工具。直接采用原理圖輸入方式,進行編譯后寫入器件中;同時可在線更改寫入內容,修改和調試簡單易行。利用MAX+PLUS Ⅱ可以對輸入輸出關系進行在線調試和仿真,開發和調試周期短而高效。MAX+PLUSⅡ的軟件設計的流程包括設計輸入、功能仿真、編譯、后仿真、編程驗證幾個部分。

本文所論述的系統已經實現并進行通信測試,在最高通信速度、通信距離、熱冗余和冷冗余實驗等測試中都取得了良好的表現。這里僅論述邏輯設計輸入和功能仿真。

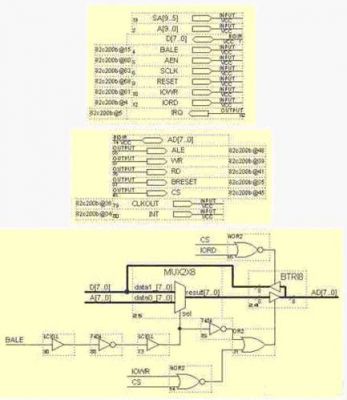

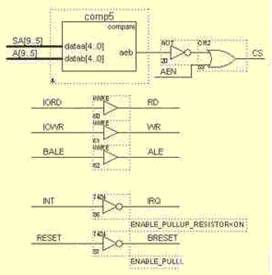

CPLD主要用于實現PC接口板的地址選擇比較器和CAN控制器到PC總線的數據轉換,其設計輸入如圖3所示。

圖3 設計輸入

其中compare完成選址功能,MUX2×8完成總線轉換。

4.仿真實驗

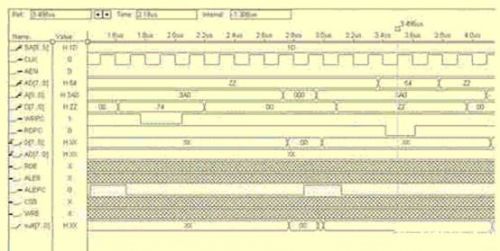

為簡明起見,這里僅給出核心的部分時序仿真圖形,如圖4所示。

圖4 核心的部分時序仿真圖形

由仿真波形可知,在PC總線的讀寫操作進行時,地址和數據很好的實現了轉換,讀寫的周期完整,觸發迅速,保證轉換的準確和迅速,滿足了設計的要求。

5.結論

可編程邏輯器件的應用已經成為現代電子電路設計中的高效方式,它可以實現高效率、可靠的設計,也可以進一步提高電路的集成度;使用它設計的CAN通信卡可以作為通信接口而滿足嵌入式系統的要求。同時,基于PC104系統的CAN通信的通信效率較高,具有較強的實時性,可以滿足工業現場高速通信的需要,也可為復雜控制系統實現實時控制提供強有力的工具。