??? 摘 要: 針對特定環境(車內空間)內的聲場重建,給出了聲效處理器的硬件設計方案。以TI公司的數字信號處理器TMS320VC5402為硬件中心,對聲音信號進行算法處理;串行16位模數轉換芯片AD1870實現對音頻信號" title="音頻信號">音頻信號的采集;串行數模轉換" title="數模轉換">數模轉換芯片AD1858完成對處理后的音頻信號的輸出。詳細敘述了TMS320VC5402和AD1870、AD1858之間的連接和時序。實驗表明,此系統可靠、穩定,為完成音頻信號的實時編解碼提供了硬件支持,使在非規范空間播放高品質立體聲音效成為可能。

??? 關鍵詞: 聲場重建? 聲效處理? 數字信號處理

?

??? 隨著現代科技的迅猛發展,立體聲音頻制作系統日臻完美,聲場的信息幾乎被全部收集。由于大部分放音聲學環境不可能像錄制環境那么完善,這些“聲音畫面”的恢復就成為研究的難點[1]。在大空間放音環境中(如露天環境),需要大量的放聲設備來完成對聲場的重建。因為這些設備占用了很多空間,阻礙了這種技術在小空間放音環境(如車內環境)下的應用。這些小空間放音環境的聲場效果的采集、傳輸、恢復與重建是音頻信號處理的研究熱點[2]。從經過傳輸混疊的雙聲道信號重建模擬聲效是電聲技術的核心,本文據此設計了一種基于數字信號處理器(DSP)的音頻實時處理的硬件系統[3-5]。本系統可以用來對立體聲音頻信號進行實時編解碼與特定環境(車內空間)下聲場效果重現處理,還可以用作同步的實時信號采集與處理。

1 聲效處理器的DSP實現

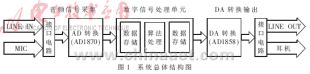

??? 本系統由TMS320VC5402[6](以下簡稱C5402)芯片、閃存(Flash)、雙通道隨機存儲器(DRAM)、模數轉換電路、數模轉換電路和電平轉換芯片等組成。系統框圖如圖1所示。

???????????????????

????由麥克或數據線傳來模擬聲音信號,首先經過ADC(AD1870)進行采集轉換,轉換后的數字音頻信號通過串行方式傳入DSP單元,DSP單元對接收的數字音頻信號進行存儲、運算、再存儲等一系列處理,處理后的數字音頻信號通過串口" title="串口">串口傳給DAC(AD1858),AD1858完成對音頻信號的恢復,把數字音頻信號轉換為模擬聲音信號,DA轉換后模擬聲音信號通過接口電路傳給耳機輸出或通過數據線由放音設備輸出。從而實現對音頻信號的采集、傳輸、恢復與重建,完成了對聲音效果的處理。

??? 其中DSP芯片C5402具有100MIPS的運算速度,配有專用的硬件乘法-累加器,可以進行高速實時運算,為音頻數字信號的實時編解碼提供了高速、可靠的硬件基礎;在對音頻信號處理時會產成緩存數據,這些數據需要占有大量的存儲空間,雙口RAM則主要負責數據的存儲;模數、數模轉換的實現在本系統中選用的是AD公司的音頻專用芯片:模數轉換芯片AD1870、數模轉換芯片AD1858。它們具有轉換速度快、采樣頻率符合聲音信號的要求、串行傳輸數據、無軟件控制寄存器、操作簡單等特點。

2 ADC、DAC與DSP的硬件連接與工作時序

??? DSP芯片C5402具有兩個獨立的多功能串口McBSP0、McBSP1,在此聲效處理系統中被用來分別與AD1870和AD1858通信。下面詳細介紹它們之間的連接和工作時序。

2.1 DSP串口與AD1870的連接

??? 在本設計中,ADC與DSP以及DSP與DAC之間的通信采用的都是串行傳輸方式,C5402芯片內部集成了兩個高速、雙向、多通道帶緩沖串行端口McBSP[7],每個串口提供了6個功能引腳和多個可程序讀寫的寄存器。C5402內部CPU通過對這些控制寄存器的讀寫完成數據的發送、接收以及對數據傳輸時序的控制。6個功能引腳分別為:

??? (1)接收、發送引腳DR、DX;

??? (2)接收、發送時鐘引腳CLKR、CLKX;

??? (3)接收、發送幀同步引腳FSR、FSX。

??? AD1870[8]是一個基于Σ-Δ技術的高速串行16位模數轉換芯片,主要用于雙聲道音頻模擬量的采集。AD1870可以以48kHz、44.1kHz、32kHz等三種采樣頻率對音頻模擬量進行采集。主要的引腳有:

??? (1)VINL、VINR——左右聲道模擬聲音信號的輸入引腳;

??? (2)BCLK、L CLK——位時鐘、左右時鐘;

CLK——位時鐘、左右時鐘;

??? (3)WCLK——字時鐘;

??? (4)SOUT——串行數據輸出引腳;

??? (5)RDEDGE——讀邊沿的極性選擇引腳;

??? (6) ——復位引腳。

——復位引腳。

?其他的引腳還有:

??? (1)CLKIN為模數轉換器AD1870的工作時鐘輸入端,fCLKIN=384×fS或者fCLKIN=256×fS;

??? (2)引腳384/ 用來選擇采用上述兩種模式的哪一種,如果384/

用來選擇采用上述兩種模式的哪一種,如果384/ =HI,則選用384模式;如果384/

=HI,則選用384模式;如果384/ =LO,則選用256模式;

=LO,則選用256模式;

??? (3)引腳S/ 、RLJUST、

、RLJUST、 用來設置AD1870數據傳輸模式,AD1870提供了8種數據傳輸模式,其中5種AD1870用做主設備,3種AD1870用做從設備。

用來設置AD1870數據傳輸模式,AD1870提供了8種數據傳輸模式,其中5種AD1870用做主設備,3種AD1870用做從設備。

??? 結合本系統的應用,經過分析把AD1870作為從設備使用,它們之間的連接如圖2所示。C5402的串口McBSP0用以和AD1870通信。C5402的主時鐘輸出引腳CLKOUT和AD1870的CLKIN引腳,這樣由DSP處理單元向AD1870提供工作時鐘。選用AD1870工作在從模式、32位數據傳送格式[5],需要做如下設置:S/ =HI、LRJUST=LO、

=HI、LRJUST=LO、 =LO。在這種模式下,要求fLRJUST=fBCLK/32,即在兩個左右時鐘LRJUST脈沖之間位時鐘BCLK要經歷32個周期。每一位時鐘BCLK周期時間傳送一位數據,共傳送32位數據,其中前16位為左聲道的數據,后16位為右聲道的數據。根據這種要求把C5402的BCLKXO、BCLKRO與AD1870的BCLK連在一起,由BCLKXO向BCLKRO和BCLK提供位時鐘信號" title="時鐘信號">時鐘信號;把C5402的BFSX0、BFSR0與AD1870的LRCLK連在一起,由BFSX0向BFSR0和LRCLK提供頻率為時鐘信號頻率的1/32的左右時鐘信號;把C5402的BDR0和AD1870的SOUT連在一起,這樣C5402就可以接收來自AD1870的數字音頻信號了,C5402的接收數據引腳接收來自AD1870串行數據輸出引腳輸出的數字音頻信號。為滿足數據傳輸要求需要對McBSP0的串口寄存器進行設置,主要設置如下:

=LO。在這種模式下,要求fLRJUST=fBCLK/32,即在兩個左右時鐘LRJUST脈沖之間位時鐘BCLK要經歷32個周期。每一位時鐘BCLK周期時間傳送一位數據,共傳送32位數據,其中前16位為左聲道的數據,后16位為右聲道的數據。根據這種要求把C5402的BCLKXO、BCLKRO與AD1870的BCLK連在一起,由BCLKXO向BCLKRO和BCLK提供位時鐘信號" title="時鐘信號">時鐘信號;把C5402的BFSX0、BFSR0與AD1870的LRCLK連在一起,由BFSX0向BFSR0和LRCLK提供頻率為時鐘信號頻率的1/32的左右時鐘信號;把C5402的BDR0和AD1870的SOUT連在一起,這樣C5402就可以接收來自AD1870的數字音頻信號了,C5402的接收數據引腳接收來自AD1870串行數據輸出引腳輸出的數字音頻信號。為滿足數據傳輸要求需要對McBSP0的串口寄存器進行設置,主要設置如下:

??? (1)串口引腳控制寄存器PCR:FSXM(11)=1;FSRM(10)=0;CLKXM(9)=1;CLKRM(8)=0

??? (2)接收控制寄存器RCR1:RFRLEN1(14-8)=0000001;RWDLEN(7-5)=010。

???????????????????????????

??? 在數據傳送期間AD1870的字時鐘WCLK一直輸出高電平,據此把C5402的通用IO口 與它連在一起,用于DSP單元檢測AD1870是否工作。另外,C5402的通用IO口XF與AD1870的

與它連在一起,用于DSP單元檢測AD1870是否工作。另外,C5402的通用IO口XF與AD1870的 直接連接,這樣就可以對AD1870進行軟件復位操作。

直接連接,這樣就可以對AD1870進行軟件復位操作。

2.2 AD1870到C5402工作時序

??? 從AD1870到TMS320VC5402的數據傳輸工作時序如圖3所示。由圖可知,在接電源后C5402通過主時鐘輸出引腳CLKOUT向AD1870的工作時鐘輸入引腳發送工作時鐘,AD1870開始工作,把模擬信號轉換為數字信號,即把左右聲道模擬聲音信號的輸入引腳VINL、VINR采集來的模擬聲音信號轉換為數字音頻信號。同時C5402的CPU通過對串口McBSP0寄存器的讀寫使串口McBSP0通過發送時鐘引腳BCLX0向C5402的接收時鐘引腳BCLR0和AD1870的位時鐘引腳BCLK發送位時鐘;通過發送幀同步引腳BFSX0向C5402的接收幀同步引腳BFSR0和AD1870的左右時鐘引腳發送左右時鐘。按照圖3所示的時序數字音頻信號由AD1870向DSP單元傳送:在第一個左右時鐘脈沖的觸發下,第一幀數據開始向DSP單元傳送,共32位數據。首先傳送的是左聲道的第一幀數據(16位);然后傳送右聲道的第一幀數據。接著出現第二個左右時鐘脈沖,第二幀數據也是按照先前的順序傳入DSP單元。數據按照這種模式連續傳向DSP單元。

?????????????????????????????

2.3 DSP串口與AD1858的連接

??? 在DSP單元處理好的音頻數字信號需要經過數模轉換,轉換成模擬聲音量輸出。本系統選用的數模轉換芯片是同為AD公司生產的AD1858數模轉換芯片。AD1858[9]是一個雙通道高速串行DA轉換芯片,用于對數字音頻信號的數模轉換。主要引腳有:

??? (1)SDATA——串行輸入引腳;

??? (2)BCLK、LRCLK——位時鐘、左右時鐘;

??? (3)MODE——輸入串行數據模式控制;

??? (4) ——上電/復位引腳;

——上電/復位引腳;

??? (5)MUTE——利用此引腳可以控制數模轉換通路的通和斷;

??? (6)MCLK——主時鐘輸入;

??? (7)OUTL、OUTR——左右聲道輸出引腳;

??? (8)MCLK為數模轉換器AD1858的工作時鐘輸入端,fMCLK=384×fS或者fMCLK= ×fS;

×fS;

??? (9)引腳384/256用來選擇采用上述兩種模式的哪一種。如果384/ =HI,選用384模式;如果384/256=LO,選用256模式;

=HI,選用384模式;如果384/256=LO,選用256模式;

?? ?(10)MODE用來設置AD1858數據接收模式,AD1858提供了二種數據傳輸模式。

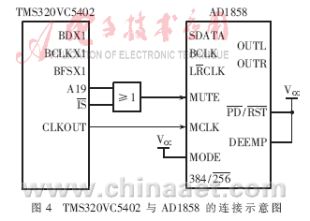

??? 與C5402的連接如圖4所示。由圖可知,C5402的串口McBSP1用以和AD1858通信。C5402的主時鐘輸出引腳CLKOUT和AD1858的MCLK引腳,由DSP處理單元向AD1858提供工作時鐘。將AD1858的引腳MODE接高電平,使AD1858工作在L-J DSP串行口模式[6]。這種工作模式要求fLRCLK≤fBLCK/16,即在兩個LRCLK脈沖之間BCLK要經歷多于16個周期。每一BCLK周期時間傳送一位數據,共傳送16位數據,在16位數據傳送完后等待下一個幀脈沖。在第一個幀同步脈沖到來時,傳送左聲道的16位數據,下一個幀同步脈沖,傳送右聲道的16位數據,這樣在LRCLK時鐘的調節下依次輪流進行傳送左右聲道的數據。根據這種要求把C5402的BCLKX1與AD1858的BCLK連在一起,由BCLKX1向BCLK提供位時鐘信號;把C5402的BFSX0與AD1858的LRCLK連在一起,由BFSX0向LRCLK提供頻率為時鐘信號頻率1/16的左右時鐘信號;把C5402的BDX1和AD1858的SDATA連在一起,這樣C5402就可以把經過算法處理的數字音頻信號傳送給AD1858了。為了使數據傳輸需要對McBSP1的串口控制寄存器進行設置,設置如下:

?? ?(1)串口引腳控制寄存器PCR:FSXM(11)=1;CLKXM(9)=1;

??? (2)發送控制寄存器XCR1:XFRLEN1=0000000;XWDLEN1=010。

??????????????????????

??? 另外,C5402的A19、IS通過或門與AD1858的引腳MUTE連接,這樣C5402就可以軟件控制數模轉換的開啟與關閉了。

2.4 C5402到AD1858時序邏輯

??? 由C5402到AD1858的工作時序如圖5所示。由圖可知,上電以后AD1858開始工作。DSP單元中處理好的音頻數字量在時鐘調節下向AD1858傳送,在第一個左右時鐘脈沖的的觸發下,數據開始傳送,AD1858根據左右時鐘先接收左聲道的一幀數據(16位)轉化為模擬量由OUTL引腳輸出;然后出現第二個左右脈沖,AD1858接著接收右聲道的一幀數據,數模轉換后由OUTR引腳輸出模擬聲音信號。接著出現第三個左右脈沖,第二幀左聲道的數據也是按照先前的順序傳入AD1858進而進行數模轉換,數模轉換依次進行下去。

?????????????????????????

2.5 電平匹配

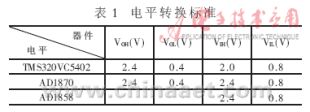

??? 在設計DSP硬件系統時,由于DSP芯片C5402的I/O工作電壓是3.3V,而ADC芯片AD1870和DAC芯片DA1858的工作電壓卻是5V,因此要分析它們之間的電平轉換標準,以滿足電壓的兼容性和接口條件。電平轉換標準從器件的電氣特性中獲得,如表1所示。

????????????????????????????????

??? 由表1可知,C5402與AD1870和AD1858的電平轉換標準是一致的,因此從C5402到AD1870和AD1858的時鐘、數據線可以直接連接。但是,由于C5402不能承受5V的電壓,因此從AD1870到C5402的數據線不能直接相連,解決的辦法是在它們之間加入一個3.3V電壓供電并能承受5V電壓的緩沖器SN74LVC245A[10]。SN74LVC245A有8路數據通道,引腳DIR用來控制數據的傳輸方向,SN74LVC245A的接口示意見圖2,基本功能如表2所示。

??????????????????????????????????

3 工作流程

??? 綜上所述,系統上電后,AD1870啟動開始模數轉換,DSP單元開始向AD1870和AD1858輸出時鐘信號,由C5402的串口McBSP0向AD1870發送左右時鐘信號,數據開始傳輸;根據位時鐘的調節,AD1870連續向DSP單元傳送數據,在DSP單元內數據經過緩存、算法處理,最后處理好的數據存在固定的數據空間;這時串口McBSP1向AD1858發送的左右時鐘信號,信號啟動向AD1858傳輸數據;同樣根據串口McBSP1送給AD1858 BCLK的位時鐘,AD1858連續接收DSP單元傳過來的數據,進行數模轉換,模擬聲音量由引腳OUTL、OUTR輸出。

??? 該系統設計已通過實驗運行驗證,達到了相應的設計要求,可用于不規范空間聲場效果的恢復。

參考文獻

[1] 惠特克 J.C.數字音頻技術寶典[M].北京:科學出版社,2004.

[2] 莫偉源.音響技術在汽車中的應用[J].音響技術,2006(1):68-69.

[3] 周霖.算法設計與系統方案[M].北京:國防工業出版社,2004.

[4] 王建平.基于DSP的多路音/視頻采集處理系統設計[J].國外電子元器件,2006,(6):27-31.

[5] 劉耦耕.語音信號變速算法及其TMS320C5402實時實現[J].中南大學學報(自然科學版),2004,35(1):117-121.

[6] TMS320VC5402 fixed-point digital signal processor.Texas?Instruments Incorporated,2000.

[7] 鄒彥.DSP原理及應用[M].北京:電子工業出版社,2005.

[8] Single-Supply 16-Bit Σ-Δ Stereo ADC AD1870.Analog?Device,Inc,2001.

[9] Stereo,Single Supply 16-,18- and 20-Bit Sigma-Delta?DACs AD1857/AD1858.Analog Device,Inc,2001.

[10] SN74LVC245 Aoctal bus transceiver with 3-state outputs.Texas Instruments Incorporated,1998.