在雷達信號處理系統中,被處理的回波信號可能來自運動目標,如飛機、艦艇、車輛等,也可能是固定背景或緩慢運動背景,如海浪和金屬絲干擾所產生的雜波。在實際應用中,從固定雜波背景中提取出運動目標回波是很重要的問題。由于固定雜波和運動目標回波的多譜勒頻移不相同,利用多譜勒濾波器濾去固定雜波而取出運動目標的回波,就可以大大改善在雜波背景下檢測運動目標的能力。由于多種高性能數字信號處理器的出現,使得可以采用軟件通過快速傅里葉變換(FFT)算法來實現窄帶多譜勒濾波器組。

本文討論的是由高速DSP芯片ADSP—TS101構成的數字式雷達信號處理器。ADSP—TS101數字信號處理器作為雷達信號處理器的核心,主要完成以下功能:一是采用快速傅里葉變換(FFT)算法來實現窄帶多譜勒濾波器組;二是對被檢測信號進行恒虛警處理。本系統在設計時比較好地發揮了高速DSP芯片ADSP-Ts101的良好性能;合理地解決了高速數據率的問題;充分地利用了芯片內部資源;降低了系統設備的復雜性,又保證了系統性能。

1 系統組成及工作原

理

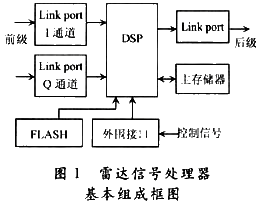

該系統選用ADSP—TS101數字信號處理器作為雷達信號處理器系統的中央處理器。處理器主頻為250 MHz,該處理器內部采用了多條分開的總線,使用多級流水線方式工作,因此具有很高的數據吞吐率和很高的執行速度。由于FFT變換要用到大量的乘法運算,而該DSP芯片可以在單指令周期內完成一條乘法指令。加上該DSP芯片的指令系統中有專用的位翻轉尋址指令,這項操作在FFT處理中是必須的,所以非常適合于做FFT處理。同時,采用浮點運算可以不必擔心運算溢出的問題,具有較高的運算精度。由ADSP—TS101數字信號處理器為核心構成的雷達信號處理器的基本組成框圖如圖1所示。

對從前級送過來的每個周期的回波數據都存入下面的矩陣的第一行,再把下一個周期回波數據存入矩陣的第二行。N個周期之后,便形成了一個N行、M列的矩陣:

FFT處理則對每一列的數據做FFT變換來實現相參積累處理,得到每一個距離單元回波信號的多普勒信息。如果第m個距離單元有目標出現,則第m列的N個數據經FFT處理后將產生與目標速度v相應的數據輸出。這樣我們就檢測到運動目標的信息。

在前后級之間傳輸數據時,利用鏈路口來進行數據傳輸。ADSP-TS101一共有4個8位的鏈路口。ADSP-TS101的鏈路口可以達到很高的數據傳輸速率,適于進行高速數據傳輸,而且電路結構比較簡單。在內部數據存儲方式上,采用乒乓存儲結構。在某一幀中,若A存儲區用于存儲前級電路傳輸過來的數據,則B存儲區中的數據供DSP進行處理,在下一幀則反過來。程序固化在FLASH存儲器中,復位后自動加載到DSP的程序存儲區中。而被處理的數據全部存放在DSP的數據存儲區中。這種分開的存儲結構加上DSP內部的多總線結構使得讀取指令和訪問數據可以同時進行,提高了運行效率。

本系統設計時利用DSP內部的DMA(直接內存訪問)功能。DMA(直接內存訪問)功能可以在不需要內核干預的情況下在2塊存儲器之間傳輸數據。DMA控制器有自己的源地址和目的地址產生器。利用DSP內部的2塊內部數據存儲區和多總線結構,在內核對一塊內部RAM中的數據進行處理時,利用DMA在另一塊內部RAM和外部存儲器之間交換數據。

2 基本工作流程

本系統在主處理程序中進行FFT積累處理,在主存儲器的輸入數據緩沖區中存儲完一個相參處理周期的數據后開始對其進行FFT處理。在主處理程序進行FFT處理的過程中,DSP響應定時中斷,在主存儲器的另一塊輸入數據緩沖區中存儲下一個相參處理周期的數據。在主處理程序完成一個處理周期后返回時切換這兩塊緩沖區,處理其中一塊緩沖區中的數據,而在另一塊緩沖區中準備數據。在ADSP-TS101芯片的內部有兩塊大小為64 k個32位字的RAM塊,由于CPU訪問內部RAM的速度比訪問外部RAM的速度快,而且在做FFT運算的過程中要多次訪問同一組數據。為了提高處理效率,最好是把數據成批地讀入到內部RAM中進行處理,處理完后再成批地送出去。

全部距離單元的數據處理完后,主處理程序讀取控制字進行判斷,看是否要做恒虛警率(CFAR)處理,如果不做則跳過這一段程序,如果做則進入恒虛警(CFAR)處理部分。恒虛警率(CFAR)處理方法采用左右距離單元平均選大恒虛警電路,采用軟件實現。通過計算被檢測單元兩側的平均雜波電平,選取其中的較大者作為檢測門限,當被檢測單元的信號超過檢測門限時,將被檢測單元的數據輸出,當被檢測單元的信號小于檢測門限時,輸出數據零。處理結果存放在輸出緩沖區中。處理程序將輸出緩沖區中的處理結果通過鏈路口輸出到后級電路。輸出結果后主程序返回。

由于整個處理系統的工作過程比較復雜,因此,軟件的設計與調試是很重要的。在處理器的工作過程中,包含了按照系統定時信號同步地與前后級之間傳輸數據,以總線并行的方式同時從外部存儲器向DSP內部存儲器輸送待處理數據和DSP對另一塊內部存儲器中已存好的數據進行運算處理,對工作方式控制字的響應與工作方式的切換等操作。這就要求在軟件結構上進行合理的設計與配置,并注意發揮DSP指令功能強和操作靈活的優點。充分利用處理器的內部資源。圖2是經簡化的處理程序流程圖。

3 結語

數字信號處理相對于模擬信號處理有很大的優越性,表現在精度高、靈活性大、可靠性好,采用具有很強編程能力的通用DSP實現數字信號處理正得到越來越廣泛的應用。