最近人工智能因為在ChatGPT等自然語言處理器方面的驚人能力而受到更多關注,但除此之外,AI還在其他多個領域慢慢產生影響,譬如將AI用于芯片設計。由于芯片設計復雜度和精度要求的不斷提高,傳統設計方法已經難以滿足需求。人工智能技術的快速發展為芯片設計帶來了新的可能性。現在越來越多的芯片產業鏈的廠商開始探索借助AI的方法來幫助芯片設計,那么芯片工程師該何去何從?

本文將介紹一些芯片巨頭利用AI技術在芯片布局中的突破,AI可以在芯片布局中發揮重要作用的原因在于其優異的圖像識別能力。

芯片布局越來越耗時

在超大規模集成電路(VLSI)中,布局(Layout)是芯片設計流程中的重要步驟之一。芯片的布局決定了物理布局中標準單元的位置,所有不同的子系統都必須以特定的方式布局,還要使信號和數據以理想的速率在這些區域之間傳播。傳統上,這項工作往往由工程師手工來完成,芯片工程師們通常會花費數周或數月的時間來不斷改進和優化他們的設計,試圖找到標準單元的最佳配置。

分析布局(Analytical placement)是目前超大規模集成電路布局的最先進技術,它可以幫助設計師在最小的芯片面積內實現高性能、低功耗和高可靠性的電路設計。分析布局通常包括三個步驟:全局布局(Global Placement,GP)、合理化布局(Legalization,LG)和詳細布局(Detailed Placement,DP)。

全局布局(GP)是指將電路元件在芯片上放置的初始階段,其目的是在不考慮細節的情況下,使得所有元件的位置相對合理,以便后續布局步驟進行。在全局布局中,采用各種算法和技術來解決面積、功耗、時序和連通性等方面的問題。在這三個步驟中,全局布局是分析布局中最耗時的部分。

合理化布局(LG)是指對全局布局的元件位置進行微調,以滿足一些硬性的約束條件,例如電路元件之間的最小距離、與芯片邊緣的距離、相鄰元件的方向等。合理化布局的目的是確保電路元件的位置符合設計規范,并且在不違反設計限制的情況下盡可能接近全局布局的解。

詳細布局(DP)是指對元件位置進行更加精細的調整,以進一步提高電路性能和減少功耗。詳細布局通常涉及更為復雜的算法和技術,例如網格化布局、全局優化和局部優化等。

但是現在隨著芯片的復雜度和密集度不斷攀升,一個先進的芯片集成了數百億個甚至數千億個晶體管,例如蘋果的M1 Ultra中集成了1140億個晶體管,AMD的instinct MI300加速器芯片中集成了1460億個晶體管,以及由此產生的功率、性能和面積 (PPA) 之間的現代復雜關系,使得芯片的布局愈發費時費力。

為了加快和優化IC設計流程,行業的芯片廠商正在探索利用深度學習方法來比人類更快、更高效地設計芯片。通過使用AI技術,芯片設計師可以將設計要求輸入到計算機中,計算機可以自動識別和處理圖像,并根據指定的規則和限制進行布局。AI技術可以更快、更準確地生成芯片布局,同時可以避免設計師在重復和繁瑣的任務中的錯誤。許多公司(包括科技行業的一些最大公司)現在都在投資AI 工具來完成一些繁重的工作。

谷歌用AI進行芯片布局

早在2021年9月,谷歌在《自然》雜志上發表了一篇文章《一種用于快速芯片設計的圖形放置方法》,聲稱利用機器學習軟件可以比人類更快地設計出更好的芯片,谷歌表示,它正在使用這款人工智能軟件設計其自主研發的TPU芯片。

谷歌在文章中寫道:“盡管經過了50年的研究,芯片布局仍然無法實現自動化,物理設計工程師需要數月的艱苦努力才能制作出可制造的布局。在不到6小時的時間里,我們的方法自動生成的芯片布局在所有關鍵指標上都優于或可與人類繪制的設計圖相媲美。”

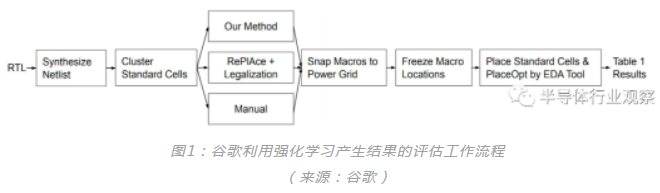

谷歌將芯片布局規劃看作為一個強化學習(RL)問題,并開發了一個基于邊緣的圖卷積神經網絡架構,能夠學習芯片的豐富和可轉移表示。具體的評估工作流程見圖1。該流程允許每個方法訪問相同的聚類網絡列表超圖,在所有方法中(盡可能地)使用相同的超參數。每種方法完成放置后(包括RePlAce的合法步驟),將宏捕捉到電網格中,凍結宏位置,并使用商業EDA工具放置標準單元并報告最終結果。

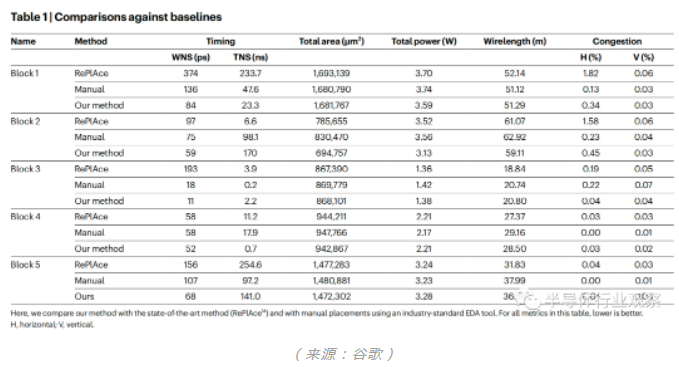

將谷歌的方法與最先進的方法(RePlAce14)以及使用行業標準EDA工具的手動放置進行比較。具體比較的指標有花費的時間、總的面積、功耗、線長等等,對于該表中的所有指標,越低越好。可以看出,谷歌的強化學習方法均優于其他兩種。

谷歌的研究團隊表示,隨著人工智能接觸到更多數量和種類的芯片,它可以通過不斷地培訓學習,會更快更好地為新芯片塊生成優化布局,雖然我們主要在谷歌加速器芯片 (TPU) 上生成優化的布局,但我們的方法適用于任何類型ASIC芯片。

英偉達DREAMPlace商業化推進有望

在加速布局方面,現有的并行化工作主要是使用分區的多線程CPU。隨著線程數量的增加,速度在5倍左右就飽和了,而且典型的質量下降2-6%。英偉達的工程師探索了利用GPU來加速分析位置布局。

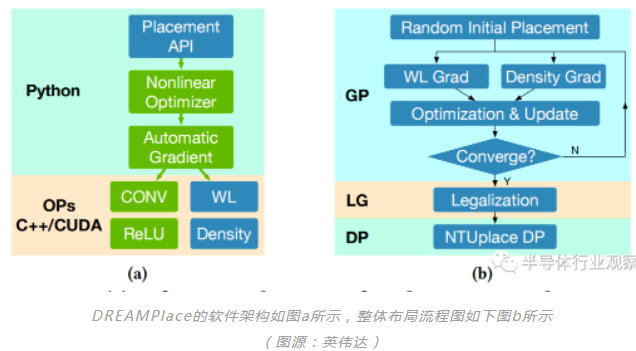

傳統的分析布局引擎開發需要花費大量的精力用C++構建整個軟件堆棧,因此,由于開發成本的問題,設計和驗證新布局算法的門檻非常高。于是,英偉達利用深度學習工具包PyTorch,通過少量的軟件開發工作,開發了一個新的具有GPU加速的開源布局引擎——DREAMPlace,這是一個比較出名的開源布局器。它通過高效的GPU實現的關鍵內核的分析布局,如電線長度和密度計算等。

該框架是用Python開發的,PyTorch用于優化優化程序和API, C++ /CUDA用于低級操作人員。DREAMPlace程序運行在基于Volta架構的40核Intel E5-2698 v4 @2.20GHz和一個NVIDIA Tesla V100 GPU的Linux服務器上,它通過拋出分析布局問題來訓練神經網絡。

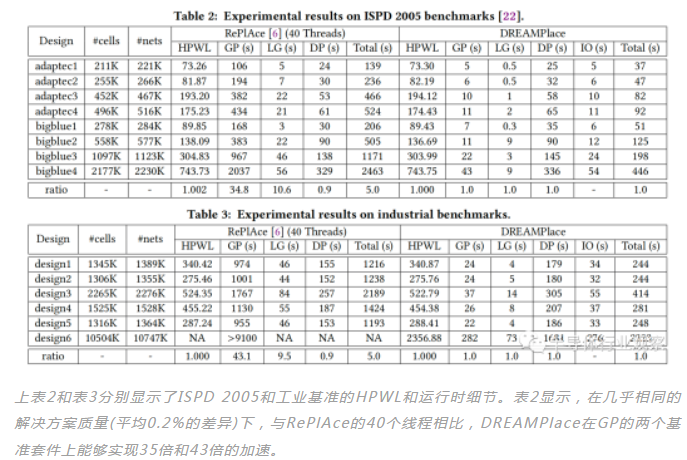

在與最先進的全球布局算法家族ePlace/RePlAce的對比中,DREAMPlace在全局布局和合理化方面實現了30倍以上的加速,且沒有理論和工業基準的質量下降。更具體的來說,它能使100萬個單元的設計在1分鐘內就能完成。英偉達探索了用于向前和向后傳播的低級操作符的不同實現(前向傳播來計算目標,后向傳播來計算梯度),以提高整體效率。

此外,DREAMPlace是高度可擴展的,可以通過簡單地編寫高級編程語言(如Python)來合并新的算法/求解器和新的目標,其工業設計可達1000萬個單元。英偉達計劃進一步研究單元膨脹的可路由性和時間優化的凈加權,以及GPU加速的詳細布局。它還可以擴展到利用多GPU平臺來進一步加速。由于DREAMPlace分離了高級算法設計符號和低級加速工作,因此它顯著降低了開發和維護開銷。英偉達的這項工作將為重新審視經典的EDA問題開辟新的方向。

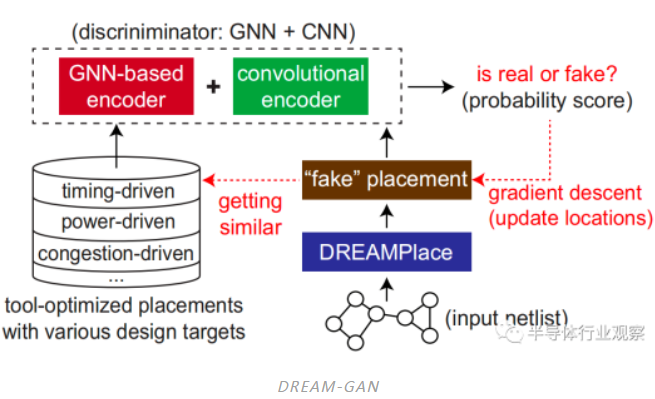

但是,由于其對線長和密度的關注有限,DREAMPlace的布局質量無法與商業工具相比,這使得它很難適用于工業設計流程。為了解決這一問題,英偉達科學家近日的一項研究文章中提出了一種新方法-DREAM-GAN,這是一種使用生成對抗學習推進 DREAMPlace的布局優化框架。DREAM-GAN的最大優勢在于,它使DREAMPlace能夠朝著工具驗證(和優化)的方向優化底層位置,而無需明確了解商業工具的黑盒算法。DREAMPlace通過優化鑒別器的輸出,提高了其商業化的位置。

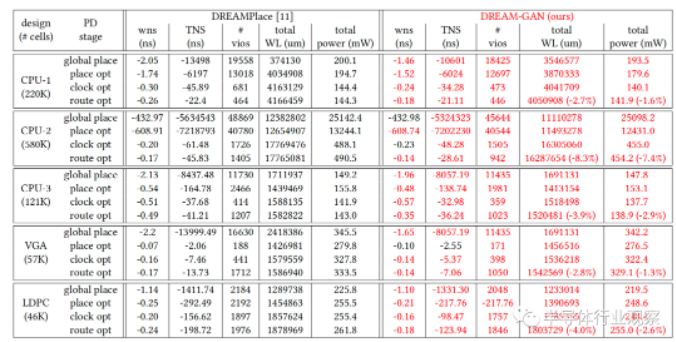

實驗表明DREAM GAN不僅在放置階段立即改善了主要的PPA指標,而且還證明了這些改進一直持續到路由后階段,在路由后階段,無線長度提高了8.3%,總功率提高了7.4%。

DREAMPlace與DREAM-GAN在各主要PD階段的詳細PPA比較結果。在這項工作中,我們使用Synopsys ICC2執行整個PD,除了全局放置由DREAMPlace(左列)或DREAM-GAN(右列)執行。在所有商業和OpenCore基準測試中,兩種方法在全局布局上的運行時差異不超過2分鐘。

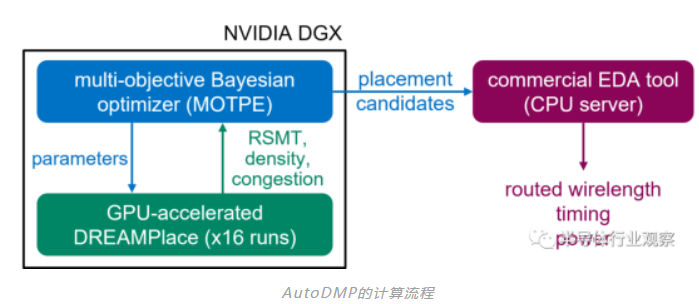

此外,Nvidia科學家近日在國際物理設計研討會上展示了AutoDMP的研究論文,AutoDMP 是使用 TILOS AI 研究所的宏布局基準進行評估的,其中包括帶有大量宏的CPU和AI加速器設計。為了進行評估,AutoDMP與商業EDA工具集成在一起,如下圖所示。首先,在NVIDIA DGX系統上運行多目標貝葉斯優化。該系統有4個A100 GPU,每個都配備了80Gb的HBM內存。生成16個并行進程以采樣參數并在優化期間運行DREAMPlace。然后,從Pareto前端選擇的宏位置被提供給運行在CPU服務器上的TILOS提供的EDA Flow。在大多數設計中,AutoDMP的PPA指標結果——線長、功率、最差負裕量 (WNS) 和總負裕量 (TNS)——等于或優于商業流程。

寫在最后

技術的發展是把“雙刃劍”。一方面,人工智能可以通過學習已有的芯片設計數據來發現規律,并通過分析數據,提供更快速、更準確的芯片設計方案。同時,人工智能技術還可以提高芯片設計的效率,縮短開發時間,減少成本。

但另一方面,隨著AI技術的不斷發展和成熟,一些沒有那么有創意的低級、平凡的工作可能會被人工智能取代。正如上文所述,在芯片布局這項工作中,過往主要是靠人工來完成,雖然目前的AI技術還有一些局限性,但隨著技術的不斷改進和突破,將或多或少的減少芯片設計過程中對手動方面的需求,雖然這提高了整體效率,但有可能會端掉部分工程師的飯碗。

不過我們也不必焦慮,回看四次工業革命,每一次工業革命都有一些工作、工人或工程師被取代,但是也會創造出新型工程師,最終提升了我們的生產力。回歸到芯片設計這一行業,AI的介入不會完全取代人工,因為就實際情況而言,行業仍需要能夠在設計過程中準確驗證和利用 AI 工具和算法的個人。這一發展對于人才的深遠影響是,提高IC設計人員在行業中的價值,使他們騰出更多的時間來專注于更復雜和更具創造性的設計方面,并最終生產出更好的產品。

利用人工智能技術來幫助設計和制造芯片已經成為大勢所趨。不僅是谷歌和英偉達,EDA軟件工具提供商Synopsys、西門子和Cadence等公司也在其最新工具中使用了AI技術,三星將AI技術引入芯片制造等等。這些AI/ML技術方法的引入,將為推進超大規模集成電路布局提供新的方向,也將成為摩爾定律再運行幾年的潛在途徑之一。

更多精彩內容歡迎點擊==>>電子技術應用-AET<<