在FPGA調試過程中,除了邏輯代碼本身的質量之外,FPGA板子上PCB走線、接插件質量等因素的影響也非常重要。在剛上板調試不順利的時候,不妨拿示波器看一下信號的質量,比如時鐘信號的質量、差分信號的質量、高速串行信號的質量等等,這是上板調試之前首先要做的一步。沒有高質量的FPGA外圍管腳信號的輸入,再好的代碼風格和規范都無濟于事。所以,調試FPGA之前一定要上示波器看一下關鍵信號的質量。

LVDS信號線間串擾問題

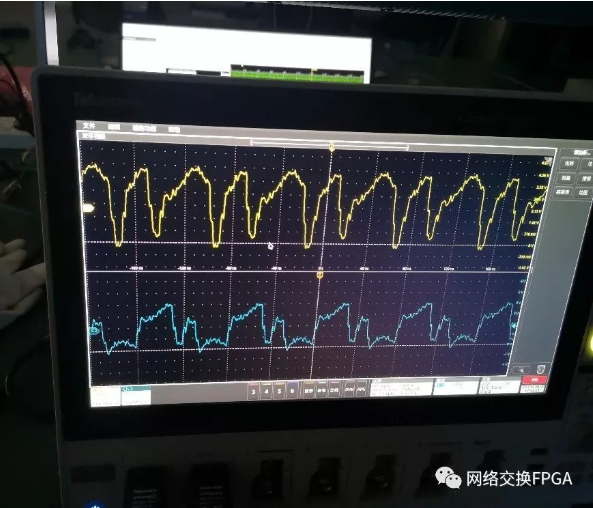

近日,在300Mbps的LVDS接口的調試過程中,出現了部分接口無法正確接收數據的現象,動用了一系列手段都無法使其老實下來踏踏實實接收數據,實可謂頑固不化。而在實驗室老師的建議和要求下,經過一番折騰之后,我們終于見到了經過LVDS驅動芯片解差分后輸入到FPGA的單端信號的真容。它是這樣的:

(上圖只抓了一位數據信號和一位時鐘信號,其實是通過兩位數據信號并行傳輸實現300Mbps的)

藍色的波形是時鐘吧,反正在上面數據信號不變化的時候還是時鐘,頻率也對,150MHz的……但是后面怎么就放飛自我了,這跟我們說好的不一樣呀……

在此之前,有必要介紹一下我們這邊調試所用硬件的情況,項目要接好多個LVDS接口,多到一個板子根本放不下,但是接口最終都是要連到一塊FPGA上的,顯然一塊FPGA只能放在一塊板子上,那這么多接口怎么辦呢,不怕,反正還有別的板子,索性就把剩余接口都放在別的板子上吧。那接口需要的LVDS32和31的收發芯片怎么辦,也沒法都放在FPGA所在的那塊板上,那就也都散開吧,LVDS接口收到的信號直接在接口旁邊的LVDS32驅動芯片上解差分,單端信號通過各個板子間的接插件傳到FPGA板上;發送則相反。所使用的接插件大概就類似于下面這種:

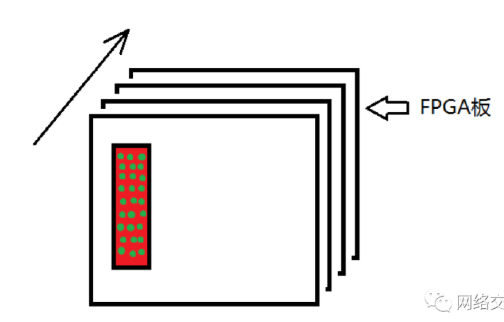

當然接插件上相鄰信號線間的間隔沒有這么大就是了,而且是三排一起。一共用了四塊板子(別的板子還有CPU啥的實現其他功能)相互疊在一起,如下圖:

綠點就表示接插件上的信號線,板間的這個接插件順著箭頭方向一直穿透到最后的FPGA板上,實現接口LVDS芯片和FPGA之間單端信號的傳輸。

硬件情況就是這樣了,我們在測試中發現無法正確接收數據的接口全部集中在距離FPGA板最遠的兩塊板子上,當把時鐘降頻之后,例如降頻到60MHz時,所有的接口都可以正確接收數據,這基本排除了FPGA代碼邏輯的問題。

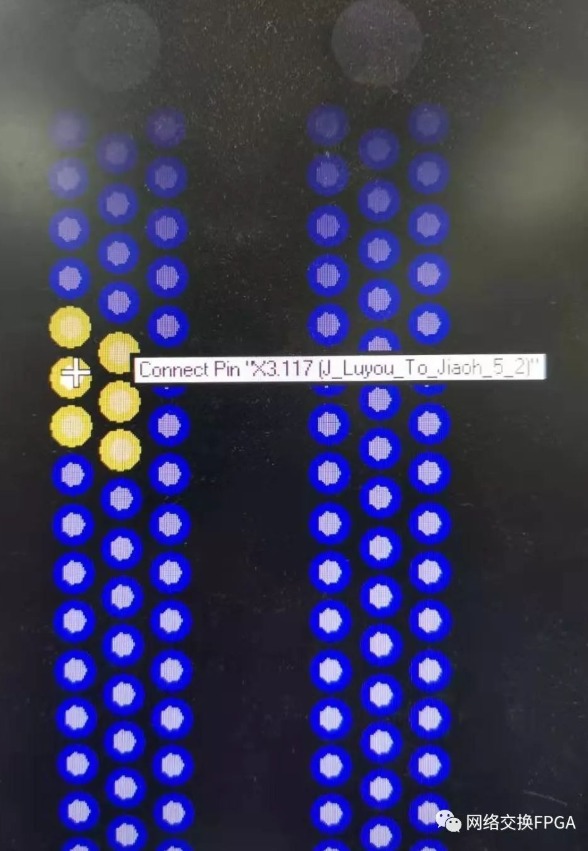

然后在與實驗室老師交流了情況之后,了解到可能是硬件這邊線間串擾的問題,然后想辦法找了從最遠的板子某個接口傳到FPGA板上單端信號的接插件管腳圖,并使用示波器幫助我們對傳輸的數據和時鐘信號進行了檢測:

上面就是板子接插件的管腳圖,上面點亮的每一列的三個信號就對應著LVDS芯片恢復出來的一位單端時鐘和兩位單端數據信號,可以看到它們是相鄰的,并且相距很近,可知硬件設計上并沒有考慮線間串擾的問題。

然后我們就使用示波器對上述管腳的信號進行了檢測,就看到了開頭的那個畫面……

自從上了研主要工作變成了寫代碼之后,感覺自己已經很久沒有接觸過硬件這塊的東西了。這次的情況花費了我們不少的時間與精力,同時我們也明白了搞FPGA開發終歸還是要對硬件有些許了解的,于是接下來我們就找了找資料,了解了一下什么是線間串擾。

線間串擾是電磁干擾的一種主要形式,當多條較長并且距離很近的導線平行傳輸信號時,其中每一條導線上的信號變化都會對其他導線的信號傳輸產生電磁干擾。

串擾的強弱受相鄰電路分布電容、互感和電路本身的阻抗影響。線間串擾對受干擾電路的影響來源于電路間的分布式電容和分布式電感引起的電磁耦合:由于每一條線路都對地存在寄生電容和電感,使得線路之間存在不同程度的耦合,當其中一條線上存在電流或者電壓變化時,相鄰線路上就會產生電磁感應或靜電感應,這就是線間串擾。線間串擾有電容耦合和電感耦合兩種形式。

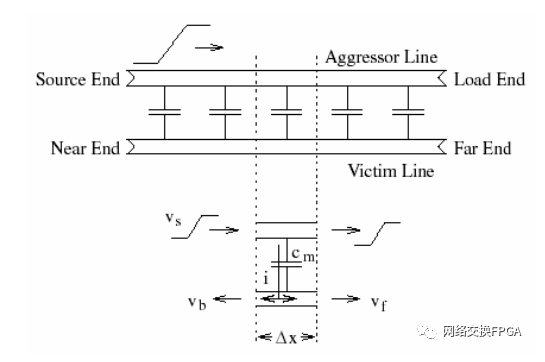

顧名思義,電容耦合是由于電子器件或線路之間存在的分布式電容,而產生電磁干擾的一種現象。導電傳輸線相互靠近時會存在一定大小的容抗,使得兩邊可以形成一個導電通路,一條傳輸線上的電壓變化會通過兩邊傳輸線之間的互容將能量耦合到另一邊,使其電位受到影響,具體影響效果如圖:

當干擾傳輸線上升沿信號Vs通過時,會在受干擾線上產生一個前向的耦合電壓Vf和后向的耦合電壓Vb,其中前向電壓產生的脈沖傳向受干擾線的遠端,后向電壓產生的脈沖傳向受干擾線的近端。

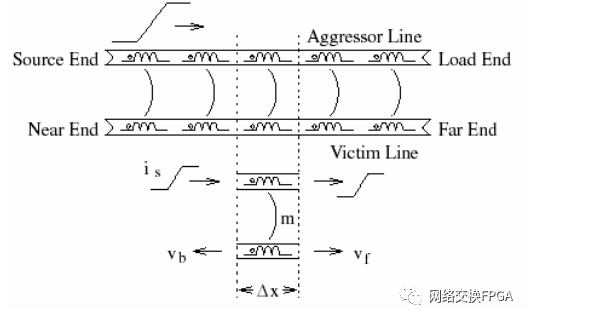

電感耦合則是由于電磁感應,一條傳輸線上的電流變化產生的磁場在另一條被干擾的傳輸線上引起感應電壓導致的電磁干擾。相對于電容耦合而言,電感耦合產生的前向電壓和后向電壓極性是相反的,效果如圖:

干擾信號在上升沿時間通過電感耦合在受干擾線上產生一個正的后向電壓和一個負的前向電壓。

其中電容耦合和電感耦合產生干擾的寬度和幅度變化是相似的,其脈沖寬度近似等于信號上升沿寬度,幅度與電壓(電流)變化斜率成正比。

電容耦合和電感耦合一般都是同時發生的,而對于非理想地平面或微帶傳輸線,電感耦合的影響要大于電容耦合。

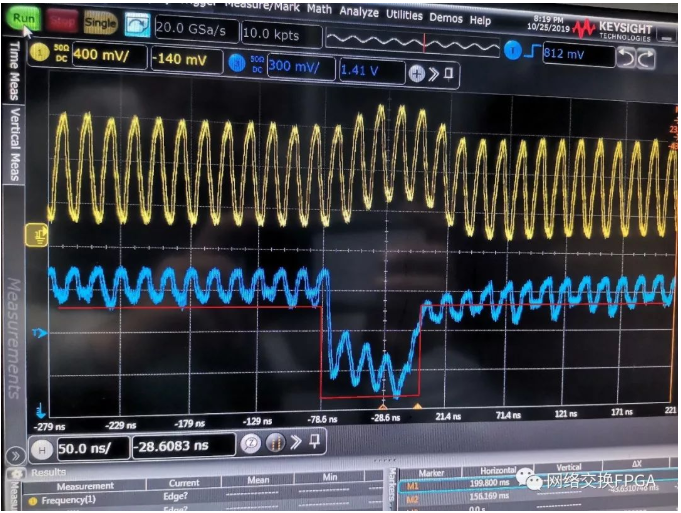

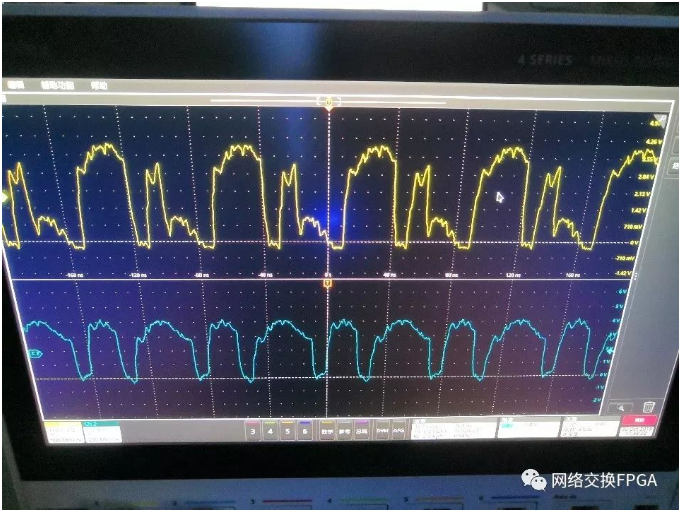

在了解了這些之后,再結合我們這邊的情況來看,從示波器的波形中我們可以看到時鐘和數據信號相互的干擾情況(為使觀察更清晰,這里以60M時鐘下波形為例)

上圖中下方藍色信號為數據信號波形,實際理想波形應如畫出的紅線所示,為一個整齊的方波,但是由于緊鄰時鐘信號線,受到時鐘信號串擾后數據波形上一直存在著幅度較小的與時鐘同頻的信號波動;而當數據信號變化自身產生較大起伏時,時鐘信號也受到影響出現了電壓的偏移。

根據時鐘和數據各自受到的影響來看,當對方電壓信號上升時,自身電壓信號便會下降,可知在該板間接插件中進行信號傳輸時,主要是電感耦合在串擾中起作用。

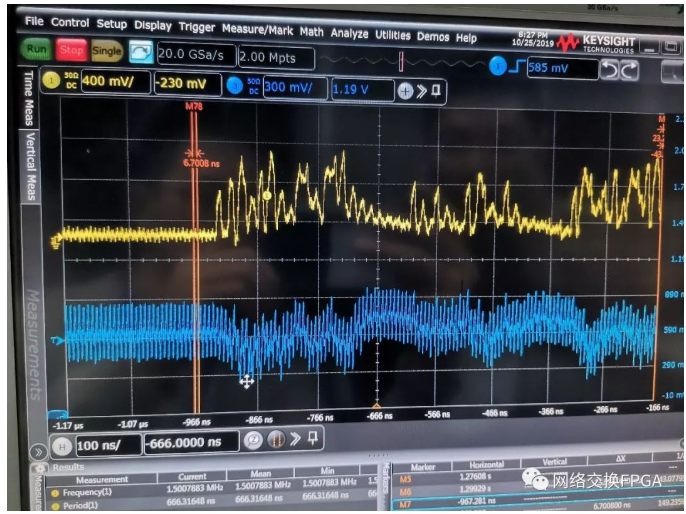

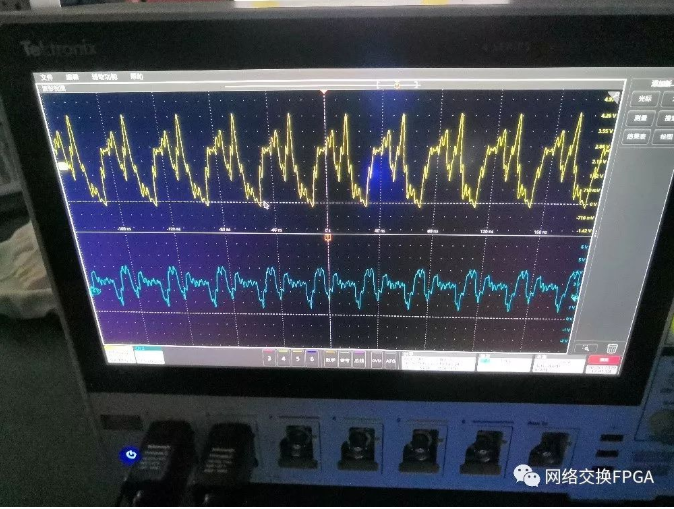

如果說上圖中時鐘頻率為60MHz時還能正常對數據信號進行采樣,但時鐘頻率增加到150MHz以上就無法正確采樣了。如下圖為時鐘頻率為150MHz時數據與時鐘的波形,已經全部亂掉了。

經過查找資料,可以用一些措施來減少線間串擾:

1. 布置電子裝置內部信號線時,盡量將其靠近接地底板,增大對地電容,從而減小串擾。

2. 在允許的空間范圍內,應盡量加大信號線與其他線之間的距離,減少線間耦合(3W原則:傳輸線中心距不少于3倍線寬時,則可保持70%的線間電場不互相干擾)。

3. 盡量縮短平行線長度,增加線間距離,如果可以,在信號線間加布隔離地線。

4. 機箱內板間的信號線越短越好。

5. 端子線進入印制板,可以在入口處增加RC去耦合電路,以便消除長線的傳輸串擾。

參考資料

https://wenku.baidu.com/view/401a805d312b3169a451a4ca.html

https://wenku.baidu.com/view/44c1d0cd27fff705cc1755270722192e453658ae.html?rec_flag=default

SpaceWire接口信號質量問題

SpaceWire總線協議支持2~200M之間速率傳輸,但是筆者在測試中目前無法實現200M進行跨板傳輸,因此通過示波器觀察在200M下D、S信號的質量,從而進一步確定到底是代碼質量存在問題,還是當前板卡的硬件質量問題。

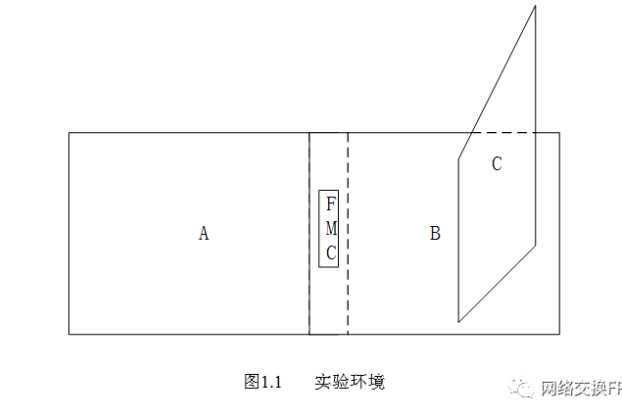

1、實驗環境

本文采用的實驗環境如圖1.1所示,該環境共有三塊板卡構成。其中A、B板卡共同構成地檢,實現將普通的以太網接口轉換為專用的SpaceWire接口,C板卡為另外一塊SpaceWire板卡。三塊板卡通過接插件互相連接。

2、實驗過程

由于SpaceWire在鏈路建立的過程中會自動發送NULL字符,因此只需將板卡上電下載代碼即可進行觀察傳輸信號的質量。為了更具有說服力,本次實驗選用10M、50M、100M、200M四種傳輸速率進行對比,由于是同一套代碼通過在線手動設置vio中寄存器的配置值實現不同的傳輸速率(使用VIVADO中VIO模擬CPU接口進行在線寄存器讀寫調試(附源代碼)),因此實驗結果具有可對比性。

2.1 10M傳輸速率

如圖2.1所示,當采用10M傳輸速率時,D、S信號質量很好,傳輸中可以正常檢測。

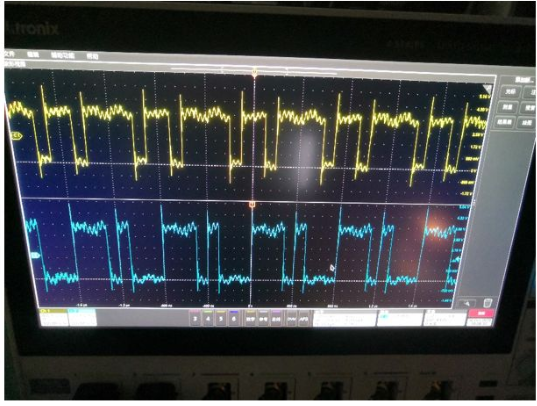

2.2 50M傳輸速率

如圖2.2、2.3所示,當傳輸速率為50M時,信號的質量有下降的表現,但對于FPGA來說,該信號質量仍然很不錯,能夠正確的采樣。

圖2.2 A板給C板發送的DS信號

圖2.3 C板給A板發送的DS信號

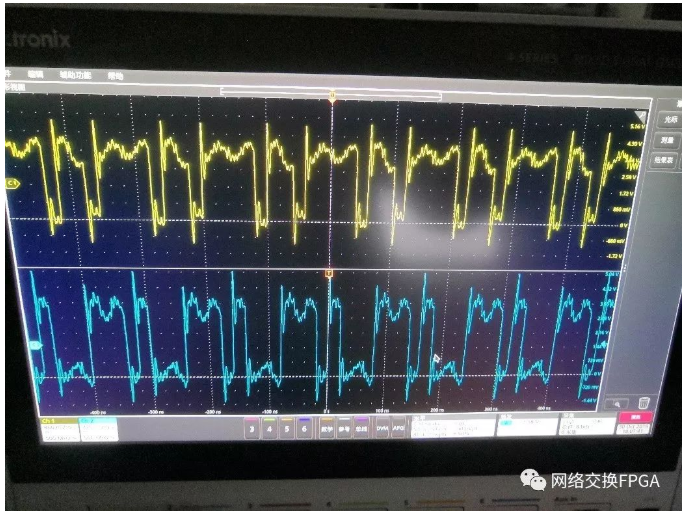

2.3 100M傳輸速率

將發送和接收速率設置為100M時,可得如圖2.4和2.5所示結果。其中圖2.4為A板給C板發送的DS信號,2.5為C板給A板發送的DS信號。可以看出,當前信號質量已經較差,但仍能正確識別與傳輸。

圖2.4 A板給C板發送的DS信號

圖2.5 C板給A板發送的DS信號

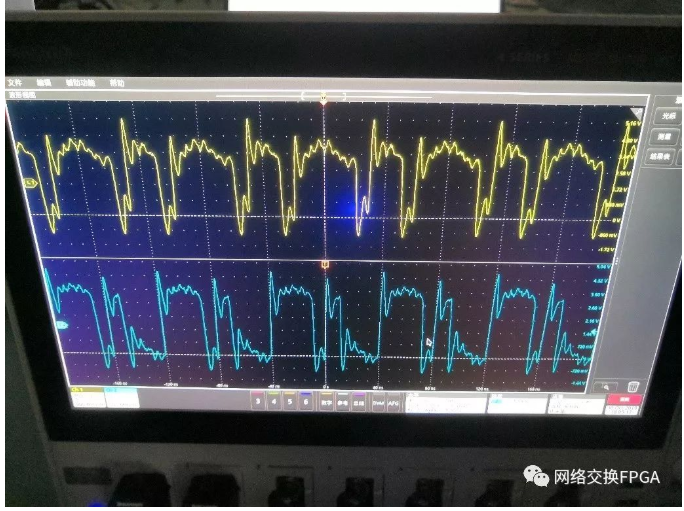

2.4 200M傳輸速率

在本文的實驗環境下,C板內部自己產生數據源,速率為200M時,可以正確接收、解析,此時通過示波器觀察到的D、S如圖2.6所示,可以看出此時的信號質量已經很差了。

圖2.6 C板自環200M下D、S信號采集結果

但是當通過A、B板和C板進行通信時,鏈路始終建立不成功,此時示波器觀察不到對應的D、S信號。

3、 實驗結果

通過上述對比可以發現,當傳輸速率為200M時,鏈路中信號質量很差,經分析顯然不是前面例子中如串擾造成的,但應該是硬件的原因造成的。具體猜測有可能有以下幾點原因造成:1、A板通過FMC接插件和B板相連,此處的走線會對信號質量產生較大的影響;2、FPGA程序中對于輸入、輸出管腳的時序約束仍有缺失;3、FPGA接收時鐘采用的是D、S異或得到的時鐘,這部分時鐘的約束缺失。歡迎看到本文的大牛告知真正的原因。

更多信息可以來這里獲取==>>電子技術應用-AET<<