Lattice Nexus是業界首個基于28 nm FD-SOI工藝的低功耗FPGA技術平臺,得益于功耗和MIPI 速度上的優勢,基于該平臺的第一款產品CrossLink-NX得到了客戶廣泛認可,主要用于嵌入式視覺領域。時隔半年,Lattice在近日宣布推出這款平臺的第二代產品——Certus-NX,具有更高的I/O密度和更低的功耗,主要面向工業自動化、通信等市場。

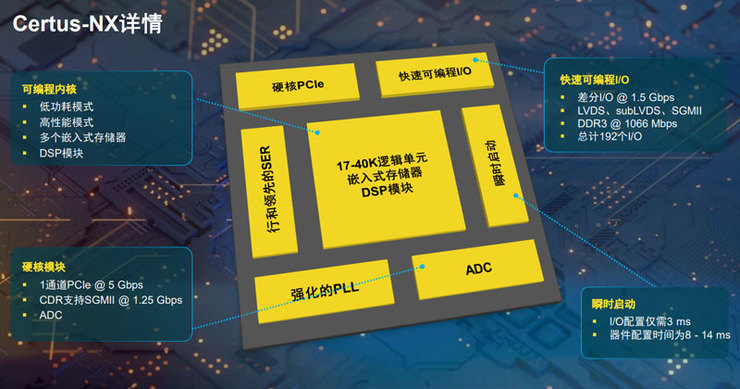

同樣是在 28nm FD-SOI 工藝平臺上打造,在邏輯單元上也均為17-40K,Certus-NX和CrossLink-NX最大的區別在哪里呢?在線上媒體溝通會上,萊迪思現場技術支持總監Jeffery Pu解釋道:“有兩點區別:第一,Certus-NX去除了硬核MIPI D-PHY,這是最大的區別,因此可以增加 I/O 的個數,這對細分市場中的一些客戶是有益的。第二,Certus-NX增添了安全認證ECDSA位流驗證,受前幾代產品的啟發,包括Lattice以前推出的 XO3D 產品,擁有 PFR 的功能,里面有很復雜的認證,我們借用這些概念放到新款產品里,這是比較明顯的一個差距。‘’

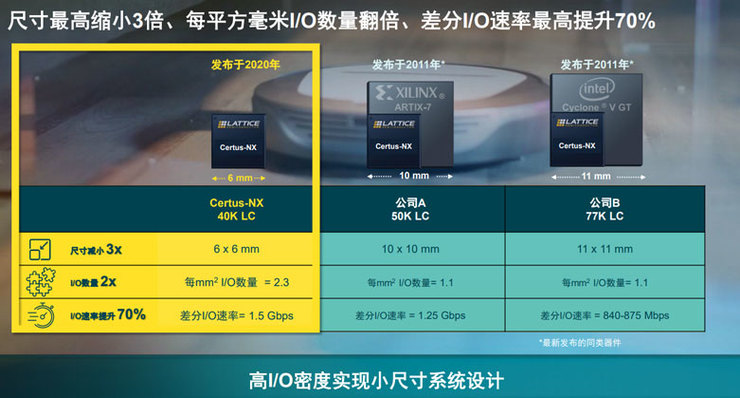

更小尺寸、更多I/O

Certus-NX 與其他兩家同類產品相比,在尺寸、I/O數量、I/O速率上都更勝一籌。

據介紹,Certus-NX FPGA可以輕松應用于小尺寸設計中,對整體設計尺寸的影響極小。例如,Certus-NX FPGA可以在36 mm2內實現完整的PCIe解決方案,相比競品FPGA尺寸縮小3倍。即便是使用Certus-NX FPGA系列的最小封裝,其每平方毫米I/O密度仍是同類FPGA競品的兩倍。1.5 Gbps差分I/O速率,相比競品FPGA性能最高提升70%。

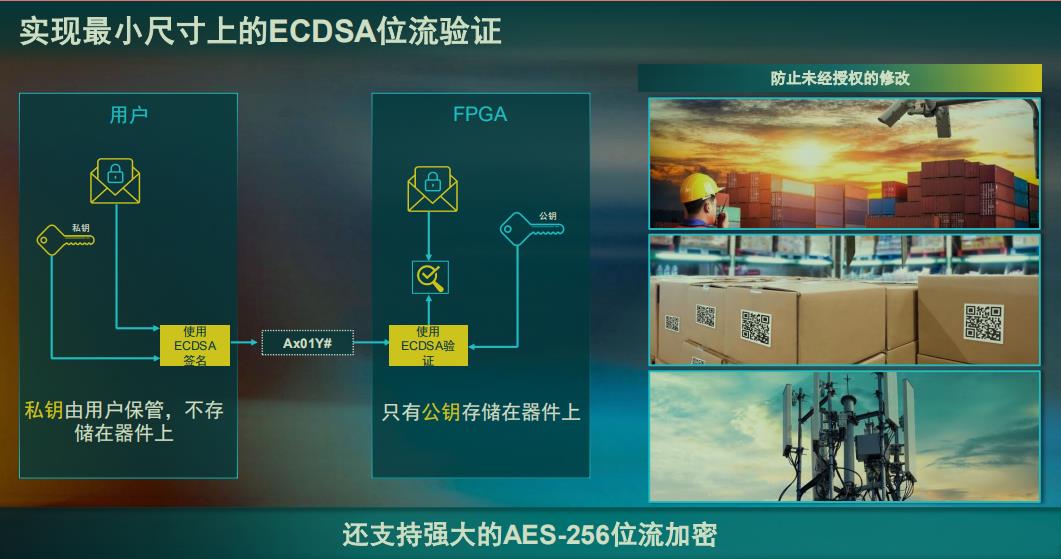

支持AES-256加密和ECDSA認證

為了保護器件的位流免于未經授權的訪問/更改/復制,Certus-NX FPGA支持AES-256加密和領先的ECDSA認證,可在設備的整個生命周期內提供保護。

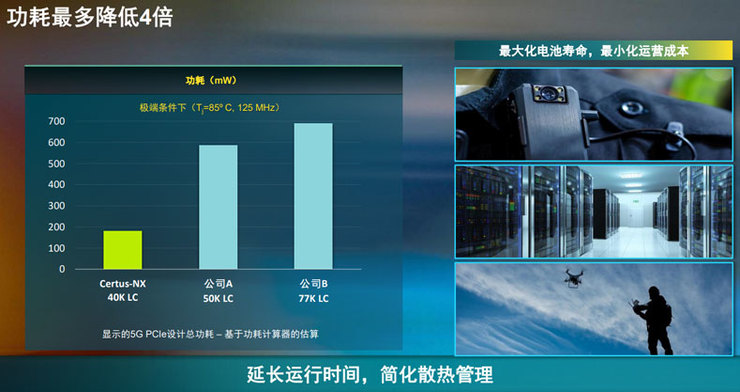

功耗降低多達4倍

在邊緣計算中,低功耗意義重大,而低功耗正是Lattice FPGA一直以來的優勢所在。Jeffery Pu表示,功耗的降低主要是FD-SOI技術帶來的,它的漏電流特別小,包括SER都是FD-SOI技術本身帶來的。與同類FPGA相比,該系列器件的功耗可降低多達4倍。

配置速度最多快12倍

全新器件還通過SPI存儲器實現超快的器件配置,其速度最該可達同類FPGA競品的12倍。單個I/O配置只需3 ms,整個器件啟動時間僅為8-14 ms(取決于器件大小)。

Jeffery Pu介紹,對于傳統 FPGA 來說,一般都是外面加一個 SPI Flash,傳統 FPGA 的快慢往往決定于 SPI 能跑多快。早些年 FPGA 能跑到 50Mbps 的速率就不錯了,現在新的 SPI Flash 可以跑到130Mbps。另外,原來的 SPI 是單通道的,現在Certus-NX使用的是 QSPI,四個通道的數據一直往里面寫,速度得以進一步提升。

軟錯誤率(SER)降低100倍

Certus-NX FPGA為工業溫度級器件,支持片上ECC和SEC。

對于安全性要求極高的工業和汽車應用而言,可靠的性能至關重要。Certus-NX 40K邏輯單元下SER達到了19.34,相比競品同類FPGA50K邏輯單元下,抗軟錯誤率(SER)性能超過了100倍。

根據Jeffery Pu介紹,由于28nm FD-SOI工藝本身的軟錯誤率(SER)就很小,比Bulk CMOS 工藝小了 100倍。加之Lattice在芯片中引入錯誤檢查和糾正 (ECC) 技術,在發現錯誤時動態改變一個比特,如果發現一個比特錯誤是可以自動改變的,如果發現兩個比特錯誤時會告訴系統,指示產生 SER 了,要重新加載,從 Flash 里重新把程序刷新一次。

為了進一步推動了FPGA開發自動化,Lattice在上半年發布了軟件方案Lattice Propel。Jeffery Pu介紹:“我們的 FPGA 在用到邊緣的時候,很多是作為 MCU 、AP 的協處理器,所以我們的軟件還是基于自己開發的軟件為主。Lattice最近推出了一套 Lattice Propel 軟件工具,包括完整的SDK。通過這套工具,基本上 10 分鐘內就可以學會整個系統開發的過程。”

Lattice已經向一部分客戶提供Certus-NX的樣片,相關工具和IP也已提供下載使用。Jeffery Pu透露,28nm FD-SOI的Nexus技術平臺的第三代產品將在不久后推出,有望為低功耗FPGA市場帶來更多驚喜。