張麗紅

(冠捷顯示科技(廈門)有限公司,福建 廈門 361101)

摘要:超高解析度圖像產(chǎn)生器用于檢測超高解析度液晶顯示器的性能和品質(zhì)。為了實現(xiàn)其便攜性和通用性,提出了一種基于FPGA與SD卡的設(shè)計方案。在檢測顯示器的質(zhì)量時需要切換各種圖像輸出,為了縮短圖像輸出的時間,采用FPGA實現(xiàn)了SD卡的SD模式。實際應(yīng)用表明,新型圖像產(chǎn)生器使用方便、數(shù)據(jù)傳輸快速可靠。

關(guān)鍵詞:FPGA;SD卡;圖像產(chǎn)生器;SD模式;硬件描述語言

0引言

隨著超高解析度液晶顯示器的發(fā)展,測量顯示屏的質(zhì)量和性能也得到了相應(yīng)的重視和關(guān)注,因此有必要研究和設(shè)計超高解析度圖像產(chǎn)生器。

目前主流的超高解析度液晶顯示器的分辨率是4K2K,即3 840×2 160。為了測試和驗證此類顯示器的性能和品質(zhì),要求圖像產(chǎn)生器產(chǎn)生相應(yīng)的4K2K測試圖像。此外,為了縮短多張圖像連續(xù)輸出的時間,就要求提高整個系統(tǒng)的帶寬,而系統(tǒng)的帶寬被限制在SD卡上,因此為了提高SD卡的數(shù)據(jù)傳輸帶寬,系統(tǒng)采用FPGA實現(xiàn)了SD卡的SD模式,從而使SD卡的數(shù)據(jù)傳輸帶寬達(dá)到25 MB/s。

所研制的圖像產(chǎn)生器不僅可以應(yīng)用于電視機(jī)生產(chǎn)企業(yè),還可以應(yīng)用于電視設(shè)備的生產(chǎn)、電視維修業(yè)等領(lǐng)域,用于觀察和評價整個電視系統(tǒng)的質(zhì)量情況。

1設(shè)計方案

圖像產(chǎn)生器提供Low Voltage Differential Signaling (LVDS)和VbyOne (VBO)輸出端口,可以產(chǎn)生多種不同分辨率的信號源,時序部分嚴(yán)格遵守CEA861標(biāo)準(zhǔn)[1]。圖像產(chǎn)生器的設(shè)計方案如圖1所示,其中SD卡作為存儲介質(zhì),Double Data Rate 3 (DDR3)作為SD卡與輸出模塊之間的緩存器,F(xiàn)PGA芯片[2]作為主控制器,采用硬件描述語言[3]實現(xiàn)了整個設(shè)計的功能。

其中主控制器采用ALTERA公司的Arria5系列FPGA芯片5AGXFB3H6F35C6來完成圖像信號的產(chǎn)生及SD卡和DDR3的控制。數(shù)據(jù)存儲采用SD卡,支持SDHC卡的High Speed模式。數(shù)據(jù)緩存則采用8塊Nanya公司的DDR3芯片,型號是NT5CB64M16FPDH,以解決低速SD卡數(shù)據(jù)讀取和高速圖像輸出之間的時序問題,最后通過LVDS或者VBO發(fā)送模塊將數(shù)據(jù)輸出到超高解析度液晶顯示器上顯示。

2硬件實現(xiàn)

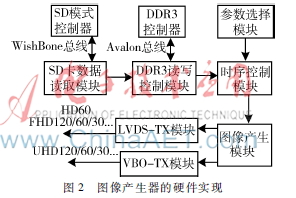

圖像產(chǎn)生器的硬件實現(xiàn)如圖2所示,它包括與SD卡連接的4 bit SD模式控制器,與8塊DDR3連接的DDR3控制器,通過I2C接口或者按鍵板發(fā)送圖像產(chǎn)生器所需參數(shù)的參數(shù)選擇模塊,與顯示器LVDS或VBO接口相連的發(fā)送模塊,及內(nèi)部相關(guān)邏輯控制單元。

2.1SD卡SD模式

FPGA通過發(fā)送、接收和監(jiān)測SD卡總線上的信號實現(xiàn)對SD卡的控制。SD卡的接口支持兩種操作模式,分別是SD模式和SPI模式。由于SPI模式是單線雙向模式,而SD模式支持四線雙向模式的高速數(shù)據(jù)傳輸,所以系統(tǒng)設(shè)計采用了4 bit SD模式,使系統(tǒng)具有較高的速度性能。

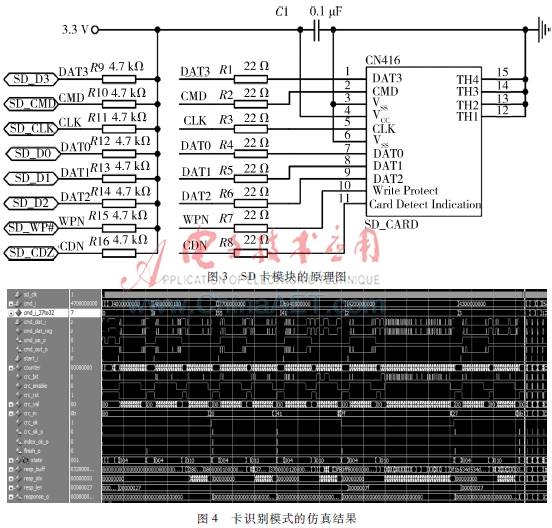

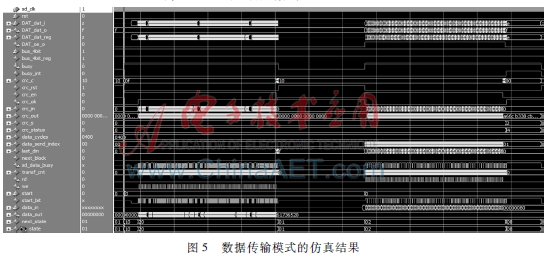

圖5數(shù)據(jù)傳輸模式的仿真結(jié)果SD卡模塊的原理圖如圖3所示,SD卡控制器基于SD4.10技術(shù)規(guī)范[4],用硬件語言進(jìn)行描述。用FPGA實現(xiàn)SD模式的SD卡控制器[5],首先由命令收發(fā)模塊、數(shù)據(jù)收發(fā)模塊及相應(yīng)的校驗?zāi)K和狀態(tài)控制模塊組成SD卡控制器;再使用這些模塊實現(xiàn)SD卡的卡識別模式和數(shù)據(jù)傳輸模式;最后用Modelsim工具對卡識別模式和數(shù)據(jù)傳輸模式進(jìn)行仿真,仿真結(jié)果如圖4和圖5所示。仿真結(jié)果符合SD卡的SD模式技術(shù)規(guī)范。

2.2DDR3緩存器

在基于FPGA的圖像處理系統(tǒng)中,常常需要用到大容量、高速度的存儲器。在主流的各種隨機(jī)存儲器件中,DDR3具有速度快、容量大、帶寬高和功耗低的優(yōu)點,而成為高速實時數(shù)據(jù)存儲系統(tǒng)設(shè)計中的首選方案。

為了縮短開發(fā)周期和簡化系統(tǒng)設(shè)計,本文采用FPGA內(nèi)部自帶的DDR3硬核控制器[6],如圖6所示,即ALTERA公司提供的基于Avalon總線[7]的DDR3 SDRAM控制器,其配置窗口如圖7所示。DDR3控制器的主要功能是完成對DDR3的初始化,將DDR3復(fù)雜的讀寫時序轉(zhuǎn)化成Avalon總線的讀寫時序,發(fā)送周期性的刷新命令來維持DDR3中的數(shù)據(jù)等。

2.3發(fā)送模塊

LVDS是一種低壓差分信號技術(shù)接口,系統(tǒng)所采用的FPGA芯片支持高速LVDS接口,LVDS的時鐘頻率一般為74.25 MHz。LVDS發(fā)送模塊的輸入信號包含RGB數(shù)據(jù)信號、時鐘信號和控制信號三大類,LVDS有4種數(shù)據(jù)格式,分別是10 bit VESA格式、10 bit JEIDA格式、8 bit VESA格式及8 bit JEIDA格式。LVDS發(fā)送模塊可以通過調(diào)用ALTERA提供的宏功能模塊ALTLVDS_TX和外部時鐘模塊Altera PLL實現(xiàn),如圖8所示。

早期的液晶顯示器采用LVDS標(biāo)準(zhǔn)傳輸圖像信號,之后隨著超高解析度液晶顯示器的發(fā)展,需要傳輸?shù)膱D像信號越來越多,要求傳輸速度高速化,且要解決傳輸線之間信號的時滯問題,為此日本賽恩電子公司提出了一種新的數(shù)據(jù)傳輸方式即VbyOne HS (VBO)。

VBO是一種傳輸圖像的數(shù)字接口標(biāo)準(zhǔn),采用一個或多個高速串行線路傳輸時鐘和數(shù)據(jù),且時鐘是疊加在數(shù)據(jù)信號上,以共模方式傳輸,每路最高速度可達(dá)到3.75 Gb/s。系統(tǒng)所采用的FPGA芯片支持高速VBO接口,VBO發(fā)送模塊主要由打包器、擾碼器、編碼器、串行器及發(fā)送鏈路監(jiān)測模塊組成,其中串行器可以通過調(diào)用ALTERA提供的宏功能模塊Arria V Transceiver Native PHY實現(xiàn),其配置如圖9所示。

3驗證與測試

開發(fā)測試平臺使用的是ALTERA的Arria5系列FPGA板子。板子上有一個SD接口,用于外接SD卡。測試平臺的實物如圖10所示。板子通過16組VBO線與超高解析度液晶顯示器連接,利用顯示器對設(shè)計進(jìn)行驗證,驗證結(jié)果如圖11所示,從圖中可以看出,該設(shè)計可以正確輸出顯示器所需規(guī)格的圖像,成功點亮屏幕。

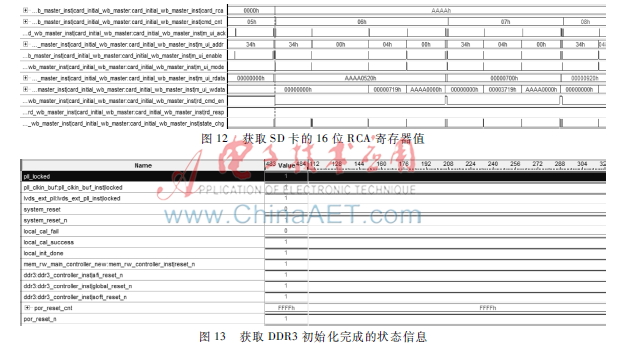

在硬件調(diào)試過程中,采用SignalTap II嵌入式邏輯分析儀觀察內(nèi)部信號的狀態(tài),如在SD卡的卡識別模式過程中獲取16位relative card address (RCA)寄存器值,如圖12所示;又如查看DDR3初始化是否完成,如圖13所示。

4結(jié)束語

本文提出了一種基于FPGA與SD卡的圖像產(chǎn)生器的設(shè)計與實現(xiàn)方案。該設(shè)計能夠?qū)D卡命令進(jìn)行自動解析和響應(yīng),在數(shù)據(jù)傳輸方式上采用了4 bit SD模式,有效地提高了SD卡的傳輸速率,從而提高了整個系統(tǒng)的傳輸帶寬。 由于設(shè)計采用了SD卡,因此圖像產(chǎn)生器尺寸小,方便攜帶。經(jīng)實際驗證圖像產(chǎn)生器可以用于檢測各種液晶顯示器,尤其是超高解析度液晶顯示器。

參考文獻(xiàn)

[1] CEA. A DTV profile for uncompressed high speed digital interfaces[EB/OL]. (20130625)[20141030].http://www.ce.org/.

[2] 吳繼華,王誠. ALTERA FPGA/CPLD設(shè)計(高級篇)[M]. 北京:人民郵電出版社,2010.

[3] 夏宇聞. Verilog數(shù)字系統(tǒng)設(shè)計[M]. 北京:北京航空航天大學(xué)出版社,2003. 圖12獲取SD卡的16位RCA寄存器值

圖13獲取DDR3初始化完成的狀態(tài)信息

[4] SD Association. Physical layer simplified specification[EB/OL]. (20130122)[20151030].http://www.sdcard.org/.

[5] 何丹,李樹國. SD存儲卡接口SD模式的FPGA實現(xiàn)[J]. 微電子學(xué)與計算機(jī),2014(1):103106.

[6] ALTERA. External memory interface handbook[EB/OL]. (201206)[20151030].http://www.altera.com.

[7] ALTERA. Avalon bus specification reference Manual[EB/OL]. (200307)[20151030].http://www.altera.com.