文獻(xiàn)標(biāo)識碼: A

文章編號: 0258-7998(2015)04-0053-03

0 引言

MEMS陀螺接口電路的數(shù)字集成化已經(jīng)成為MEMS陀螺發(fā)展的一個(gè)最熱門的方向,所以高性能模數(shù)和數(shù)模轉(zhuǎn)換器對于數(shù)字陀螺接口電路的集成就變得格外重要[1]。如圖1所示,在一個(gè)數(shù)字陀螺的經(jīng)典系統(tǒng)結(jié)構(gòu)中,DAC擔(dān)負(fù)著將DSP處理后的數(shù)字信號轉(zhuǎn)換為模擬信號的作用,然后將模擬信號反饋給陀螺,從而實(shí)現(xiàn)閉環(huán)數(shù)字控制的功能,用來保證整個(gè)系統(tǒng)的穩(wěn)定。相對于傳統(tǒng)的耐奎斯特?cái)?shù)模轉(zhuǎn)換器而言,Sigma-Delta數(shù)模轉(zhuǎn)換器能夠?qū)崿F(xiàn)更高的精度,這對于提升MEMS數(shù)字陀螺系統(tǒng)的整體性能而言具有非常重要的現(xiàn)實(shí)意義[2]。此外,針對于多位量化數(shù)字調(diào)制器的內(nèi)部DAC不匹配導(dǎo)致的非線性問題,對DWA模塊進(jìn)行了改良設(shè)計(jì),并且通過FPGA驗(yàn)證,得到了預(yù)期的結(jié)果。

1 Σ-ΔDAC結(jié)構(gòu)

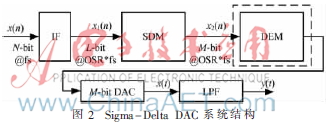

一個(gè)典型的Σ-Δ DAC的系統(tǒng)結(jié)構(gòu)如圖2所示。輸入數(shù)字信號x(n)是經(jīng)過耐奎斯特頻率fs采樣得到的。數(shù)字插值濾波器的主要功能是對數(shù)字信號進(jìn)行二次采樣,從而提高數(shù)字信號的采樣頻率,x1(n)的位數(shù)L大于或等于x(n)的位數(shù)N。信號x1(n)通過Sigma-Delta數(shù)字調(diào)制器進(jìn)行量化來降低輸出精度,并抑制量化噪聲。當(dāng)輸出的位數(shù)M>1時(shí),內(nèi)部M位DAC由于器件之間存在失配誤差,會產(chǎn)生非線性問題[3]。因此需要采用動(dòng)態(tài)單元匹配技術(shù)(DEM)減小內(nèi)部M位DAC的非線性[5-7]。

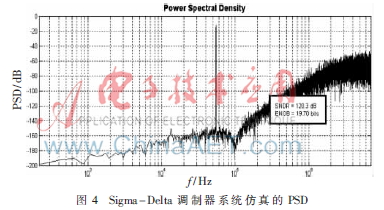

綜合分析各個(gè)結(jié)構(gòu)的優(yōu)缺點(diǎn),折中考慮后,本文中的Σ-Δ數(shù)字調(diào)制器最終采用了三階四比特量化的單環(huán)前饋結(jié)構(gòu)(CIFF)。圖3為NTF經(jīng)過零點(diǎn)優(yōu)化后的最終結(jié)構(gòu),經(jīng)過零點(diǎn)優(yōu)化的結(jié)構(gòu)其量化噪聲能夠顯著降低,并且穩(wěn)定性也得到顯著提高。圖4為系統(tǒng)結(jié)構(gòu)的仿真結(jié)果。當(dāng)輸入信號為頻率為50 kHz、歸一化信號幅度為0.5的正弦波,系統(tǒng)的采樣頻率為12.8 MHz時(shí),得到輸出功率譜密度(PSD)。在100 kHz的信號帶寬內(nèi),系統(tǒng)的SNDR能夠達(dá)到120.3 dB,有效位數(shù)達(dá)到19.7位,滿足數(shù)字陀螺的性能要求。

2 改進(jìn)型DWA

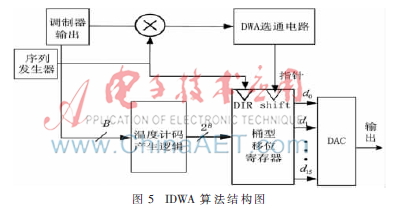

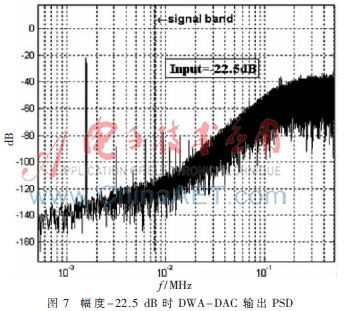

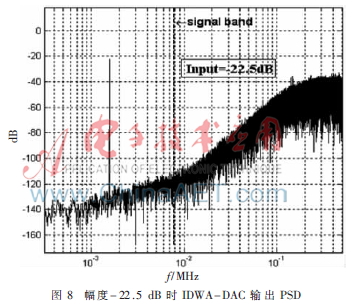

動(dòng)態(tài)元單元匹配技術(shù)(DEM)是一種對D/A轉(zhuǎn)換器中溫度計(jì)碼線性化處理的方法,而數(shù)據(jù)加權(quán)平均(DWA)由于具有整形效果明顯、硬件實(shí)現(xiàn)簡單、節(jié)省硬件開銷等特點(diǎn)而最為常見。向調(diào)制器輸入小幅度的信號時(shí),數(shù)字調(diào)制器的輸出代碼值將大部分集中在中間值及其附近,這相當(dāng)于連續(xù)向內(nèi)部DAC輸入固定直流值。因此,動(dòng)態(tài)匹配單元的誤差將會周期化,即在基帶內(nèi)產(chǎn)生噪聲。本文使用的改進(jìn)的DWA(IDWA)的基本思想是通過增加單元DAC的數(shù)量[8],使得單元DAC的數(shù)量大于調(diào)制器的量化等級,以此來解決上述問題。圖5是IDWA的算法結(jié)構(gòu)圖。圖6 是IDWA中的單元選擇邏輯(ESL)模塊框圖。IDWA與傳統(tǒng)DWA模塊相比還具有一些優(yōu)點(diǎn)。首先IDWA系統(tǒng)反饋回路中的輸入以及求和端均可以使用B位有符號信號,而不必為DWA中的B+1和B+2位有符號信號;其次是在DWA系統(tǒng)反饋回路的反饋信號中,不必使用求余算法,降低了系統(tǒng)結(jié)構(gòu)的復(fù)雜性。在Matlab中建立DWA-DAC和IDWA-DAC系統(tǒng),進(jìn)行仿真對比。當(dāng)向兩種系統(tǒng)輸入幅度為-2.5 dB、頻率為20 kHz的信號時(shí),都能完成失配誤差整形,產(chǎn)生的雜波被整形到高頻處。但如果幅度降低到-22.5 dB時(shí),情況會變得不同。圖7和圖8分別是輸入幅度-22.5 dB時(shí)的DWA-DAC輸出功率譜和IDWA-DAC輸出功率譜。由圖中可以看出DWA-DAC輸出功率譜信號帶寬內(nèi)出現(xiàn)了寄生雜波,產(chǎn)生的失真將會降低調(diào)制器的動(dòng)態(tài)范圍,而相同條件下的IDWA-DAC仍然能夠很好地完成失配誤差整形,保證了帶寬內(nèi)的信號精度。因此通過對比可以發(fā)現(xiàn),當(dāng)向數(shù)字調(diào)制器輸入小幅度信號時(shí),相比于典型的DWA算法,IDWA算法能夠有效提高調(diào)制器的動(dòng)態(tài)范圍。

3 仿真結(jié)果

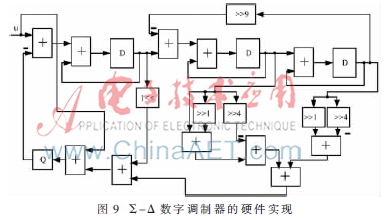

本文中Sigma-Delta數(shù)字調(diào)制器的硬件實(shí)現(xiàn)如圖9所示,其中的各個(gè)參數(shù)都采用了CSD編碼優(yōu)化,可以大幅度地減少硬件的消耗。

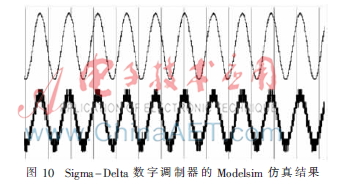

對調(diào)制器進(jìn)行Verilog代碼實(shí)現(xiàn),整個(gè)系統(tǒng)在modelsim下的仿真結(jié)果如圖10所示。從波形上可以看到,此結(jié)構(gòu)實(shí)現(xiàn)了多位量化Σ-Δ數(shù)字調(diào)制器的功能。

4 FPGA驗(yàn)證結(jié)果

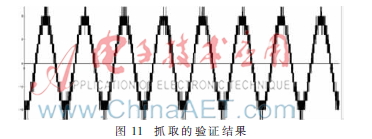

最后利用FPGA進(jìn)行Σ-Δ數(shù)字調(diào)制器的綜合和驗(yàn)證,本文使用的FPGA芯片是Xilinx公司Spartan3E系列XC3S500E產(chǎn)品。經(jīng)過綜合后輸入頻率50 kHz的正弦波,采樣率為12.8 MHz,經(jīng)過FPGA處理之后,圖11為利用Chip Scope Pro抓取的波形。將Σ-Δ數(shù)字調(diào)制器輸出數(shù)據(jù)從FPGA中導(dǎo)出,對導(dǎo)出的數(shù)據(jù)進(jìn)行FFT運(yùn)算,二次諧波小于-140 dB,三次諧波小于-135 dB,最大信噪失真比能達(dá)到120 dB,有效位數(shù)能達(dá)到19位以上,滿足設(shè)計(jì)要求。

5 結(jié)束語

本文設(shè)計(jì)了一款三階四位量化的Σ-Δ數(shù)字調(diào)制器,并且對DWA結(jié)構(gòu)進(jìn)行了算法改進(jìn)。最后利用FPGA驗(yàn)證了設(shè)計(jì)的正確性,達(dá)到了設(shè)計(jì)要求,實(shí)現(xiàn)了預(yù)期的設(shè)計(jì)目標(biāo)。

參考文獻(xiàn)

[1] LIN L,LIU D,CUI J,et al.Digital closed-loop controller design of a micromachined gyroscope based on auto frequency swept[C].IEEE International Conference on NEMS,2011(6):654-657.

[2] GE F,LIU D,LIN L,et al.Fast self-resonant startup pro-cedure for digital MEMS gyroscope system[C].The 7th IEEEInternational Conference on NEMS,March 2012:669-672.

[3] RODJEGARD H.A digitally controlled MEMS gyroscope with 3.2 deg/hr Stability[C].Digest of Technical Papers.IEEE Transducers’05,The 13th International Conference on Solid-State Sensors,Actuators and Microsystems,June 2005(1):535-538.

[4] Li Bingxin.Design of multi-bit sigma-delta modulators for digital wireless communications[D].PhD dissertation,Royal Institute of Technology,2003:40-45.

[5] WELZ J,GALTON I.Necessary and suffcient conditions for mismatch shaping in a general class of multibit DACs[J].IEEE Trans.CircuitsSyst.II,Analog Digit.Signal Process.,2002,49(12):748-759.

[6] Sun Nan.High-order mismatch-shaped segmented multibit Σ-Δ DACs with arbitrary unit weights[J].IEEE Transac- tions on Circuits and Systems I,F(xiàn)eb.2012,59(2):295-304.

[7] GALTON I.Why dynamic-element-matching DACs work[J].IEEE Transactions on Circuits and Systems II,2010,57(2):69-74.

[8] VADIPOUR M.Techniques for preventing tonal behavior of data weighted averaging algorithm in sigma delta modulator[J].IEEE,Circuits and Systems II,2000,47(11):1137-1144.