摘 要:一種通用的基于CPLD" title="CPLD">CPLD的片內振蕩器的設計方法,其振蕩頻率" title="振蕩頻率">振蕩頻率能在一定范圍內調整。本設計使基于CPLD的片上系統" title="片上系統">片上系統設計無需外部時鐘源,加大了系統的集成度并降低了設計成本。

關鍵詞:片內振蕩器 復雜可編程邏輯器件 片上系統

在絕大部分數字系統設計中,時鐘是不可或缺的部分,通常采用外接有源或者無源振蕩器來提供時鐘信號。外接時鐘的優點是性能穩定,設計簡便;缺點是會增加電路板面積,而且高頻設計時對電路板布線和加工的要求比較嚴格,可能增加系統成本和設計難度。基于可編程邏輯器件FPGA/CPLD的設計提供了另外一種選擇,即采用片內的可編程資源實現振蕩器功能。這種設計可以將振蕩部分同時集成到FPGA/CPLD中,減少了外部資源的使用。

環形振蕩器是最簡單的振蕩器設計方法,在分立器件和專用集成電路(ASIC)設計中一直受到關注[1,2,3]。但是在這類設計中,振蕩頻率隨電壓變化的特性使其應用受到限制,所以要在工藝或電路設計方面考慮振蕩頻率的穩定問題[2][3]。隨著電路制造技術的發展,穩壓電路已經物美價廉;另外,FPGA/CPLD廠商為用戶在片內預設了一些特定模塊,為振蕩器的片內實現提供了方便。如Altera公司的MaxII系列CPLD芯片,允許用戶通過軟件Quartus II的MegaWizard Plug-in Manager功能來調用系統提供的參數化模塊庫(LPM)。其中的IO/MAXII Oscillator[4]模塊即是一個能在芯片內部實現片內振蕩器的軟核,其工作頻率范圍為3.33MHz~5.56MHz,用戶不可以調整工作頻率。在做仿真應用時,可選擇3.33或5.56MHz;在實際應用中,會自動給出3.33~5.56MHz范圍內的振蕩頻率。該片上振蕩器模塊只能下載在MaxII系列芯片內的用戶閃存存儲器(UFM)上,振蕩輸出可以驅動芯片引腳和內部邏輯,該UFM資源一旦作為振蕩器使用,便不能再實現并聯接口(PIO)、串連接口(SPI)和IIC接口等其他功能。

本文介紹一種通用的基于CPLD的片內振蕩器設計方法,它基于環形振蕩器原理,只占用片上普通邏輯資源(LE),無需使用專用邏輯資源(如MaxII中的UFM),從而提高了芯片的資源利用率;振蕩頻率可在一定范圍內調整,振蕩輸出可以驅動內部邏輯和外部器件引腳。本設計有較大的通用性,可方便地在不同CPLD器件間移植,使一些基于CPLD的片上系統(SoC)設計無需使用外部時鐘信號源,從而降低設計成本和難度,增加系統集成度。通過在Altera公司的MAX7000系列EMP7128LC84-15芯片上的實驗說明實現的方法。實驗實現的頻率范圍在8MHz~62MHz。仿真和硬件測試結果表明了該設計方法的正確性和可行性。

1 基于CPLD的片內環形振蕩器

環形振蕩器原理如圖1所示。由奇數個非門組成的環形非門級聯串使電路處于無穩定狀態,靜態下任何一個非門的輸入和輸出都不可能穩定在高電平或低電平,而只能處于周而復始的高低電平轉換狀態,從而產生自激振蕩[5]。振蕩周期為T=2Ntpd,其中N是非門的個數,tpd是每個非門的傳輸延遲時間,改變電路中非門的數量可以改變電路的振蕩頻率。

圖1所示的環形振蕩器即使采用電路原理圖輸入,經電子設計自動化(EDA)軟件綜合后,也得不到對應的電路結構。實際上,EDA綜合工具不是從電路結構出發,而是從電路輸入和輸出的邏輯關系出發給出綜合結果,所以,奇數個非門的級聯將被綜合為一個非門,而偶數個非門的級聯被綜合為一個緩沖或一條聯線。為能在CPLD器件中實現圖1的環形振蕩器結構,本文將圖1中單端口輸入元件改成二端口輸入元件,即用二輸入與非門代替圖1的第一個非門,其余偶數個非門則用二輸入與門代替,二端口元件的一個輸入端口連接上級輸出,另一輸入端口作為控制端引出。振蕩器正常工作時控制端全部置高電平。采用Synplify Pro 7.7綜合后的原理圖如圖2所示。該電路完全可實現圖1的功能。

為了保證正反饋,圖1結構的非門級聯必須是奇數個。圖2中的與非門起到反相作用,其他與門則起延時緩沖的作用。可以通過改變門的數量以及選擇門的種類(與門、與非門等)改變osc輸出端的振蕩頻率,而不受“奇數”個門的限制,只要保障第一個門得到正反饋就可以產生振蕩。而圖1的結構必須改變偶數個非門才能達到改變振蕩頻率的目的,因而圖2結構在CPLD芯片中實現時可以節省邏輯資源。控制端oscena[n-1,0]為振蕩使能控制端,置高電平時,與非門的輸入和輸出在緩沖級聯鏈的反饋作用下產生自激振蕩,振蕩器正常工作;控制端的任意一位置零使振蕩器停振。所以oscena既可單獨使用,也可互聯后作為一個端使用。實驗證明,圖2結構能夠保證門延時的等間隔特性。

2 CPLD片內振蕩器的實現和優化

2.1 CPLD片內振蕩器的實現

基于上述方法的片內環形振蕩器設計有很大的通用性,可在不同CPLD芯片間方便地移植。本文以Altera公司的MAX7000S系列CPLD芯片的實現和測試為例說明。MAX7000S系列基于先進的多矩陣構架設計,采用CMOS工藝制造,容量高達256個邏輯單元LE(Logic Element),每16個宏單元組成一個邏輯陣列塊LAB(Logic Array Block),速度達3.5ns的管腳到管腳延時,同時支持多種I/O電壓標準。

從EDA軟件綜合后的報告可以看出,圖2所示電路中每個門占用了一個邏輯單元。也就是說,電路內LE的延時將作為門的延時tpd,而且需要將振蕩使能端引出到I/O引腳,當所實現振蕩頻率較低時,需要較多的門電路單元,這將占用一定的邏輯和引腳資源,從而降低芯片資源的利用率,所以在低頻情況下使用時,要綜合考慮系統需要的振蕩頻率,盡量用較少的門電路實現環形振蕩器,以提供較高振蕩頻率,再設計分頻電路以取得合適的振蕩頻率,從而提高芯片的資源利用率。綜合器的這一處理,從客觀上保證了設計者可以選擇不同的門來實現圖2的結構,仍然可以保證振蕩間隔的一致性。實驗也證實了這個結果。

2.2 電源電壓的影響

電壓會影響振蕩電路的工作頻率[6],電壓增大會導致電路振蕩頻率增加,反之振蕩頻率減小。CPLD芯片一般有兩個相對獨立的供電端口,即核心電壓(VCCINT)和引腳電壓(VCCIO)。其中核心電壓給芯片內部可編程邏輯電路資源提供電源,引腳電壓為芯片的I/O引腳提供電源,以適應各種輸出標準(如LVCOMOS、LVTTL、SSTL-2、SSTL-3等)。對振蕩頻率有影響的是CPLD芯片的核心電壓,對此電壓應采取穩壓措施,穩壓措施要視不同的應用要求而定。最簡單的措施是采用高性能的穩壓芯片給CPLD芯片分別提供兩部分電壓。隨著半導體技術的發展,簡單而廉價的穩壓芯片已具有較高的性能,如National公司的LM2678系列芯片[7]在有效輸入變化范圍內,穩壓輸出誤差在±2%以內。

2.3 CPLD片內振蕩器優化

通過EDA軟件對設計做優化有可能提高所設計的振蕩器的性能,減少對CPLD片內資源的占用。當采用MAX+plusII10.2軟件設計時,軟件優化開關設置為:(1)本設計選用MAX系列芯片,故選擇對該芯片的多層綜合選項(Multi-Level Synthesis for Max5000/7000/9000Device)。(2)在面積和速度優化選項中,選擇對面積的優化,使振蕩器部分盡可能分配到同一個LAB中。(3)打開“Slow Slew Rate”以降低開關噪聲,打開“XOR Synthesis”以減少芯片面積的占用。

3 電路仿真及測試結果

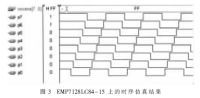

本文以Altera公司的MAX+plus II 10.2為設計工具,在MAX7000S系列芯片上實現并測試。圖3為選用EMP7128LC84-15芯片的時序仿真結果。其中 p0~p7分別為環形振蕩電路中單個門之后的電路節點;oscena[7...0]為各延時門電路的控制端(即所有二輸入門中多余的輸入端)。

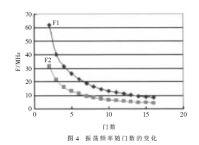

表1列出了以EPM7128LC84-15為目標芯片、采用Tektronic TDS2012示波器對用不同門數實現的片內振蕩器的測試數據。F1和F2分別表示片內振蕩器輸出和二分頻輸出的測量數據。圖4給出了測量數據的曲線。

表1數據表明,通過增加門電路的數量可以有規律地減小振蕩電路的工作頻率,由每個邏輯單元實現的門電路單元延時tpd在7.5~10ns之間。

本文介紹的基于CPLD的片內振蕩器設計方法,在改變該振蕩器電路中門電路數量時,可以有規律地將振蕩頻率控制在8MHz~62MHz范圍內。振蕩器的片內設計使基于CPLD的片上系統(SoC)設計無需外接時鐘信號源,加大了系統的集成度并降低了設計成本。本方法有很大的通用性,可以方便地在不同CPLD芯片間移植。仿真和測試數據表明該設計方法具有正確性和可行性。

參考文獻

[1] 高永紅,徐婕.一種實用的電壓控制環形振蕩器.微電子技術,2002,30(6):41-42.

[2] 徐志偉,鄭增鈺.一種結構新穎的壓控環形振蕩器.微電子學,2000,30(3):193-194.

[3] 胡二虎,汪東旭.一種頻率穩定的集成CMOS環形振蕩器.微電子學,2003,33(3):259-260.

[4] Alter Corporation.Max II Device Handbook.www.altera.com.cn,2005

[5] 清華大學電子學教研組.數字電子技術基礎(第四版).北京:高等教育出版社,1998.

[6] 王博,郭林.CMOS環形振蕩器的噪聲分析.微電子學,2003,33(3):221-223.

[7] National Semiconductor.LM2678 Simple Switcher High Efficiency 5A Step-down Voltage Regulator Specification.www.national.com,1998.