作為DSP 芯片與外界交換數據的重要關口,外擴存儲器" title="存儲器">存儲器接口" title="接口">接口的優劣程度直接影響著DSP 的適應性和控制功能,同時,高性能、靈活性強的外部存儲器接口也是利用DSP 搭建圖像采集處理系統的重要保證。基于上述原因,本文提出了一種基于CPLD 的VC5402" title="VC5402">VC5402 存儲器擴展方案,此方法具有接口靈活、調試方便的優點。

圖像采集處理系統中資源的配置情況

為了更方便地了解VC5402 與外部存儲器的接口設計,本文首先介紹在設計的圖像采集處理系統中VC5402的資源配置狀況。

VC5402 有3 個比特位(MP/ MC # ,OVL Y,DROM)共同影響著存儲器的結構,用戶可以根據需要修改PMST的值來配置存儲空間。

本文采用了微處理器模式,設置MP/ MC # = 1 ,片上4 k 字的ROM 不映射到程序區,即ROM 不可訪問。設置OVL Y= 0 ,片內16 k 字的RAM 不映射到程序存儲器,使64 k 字的程序存儲空間全部配置成外部存儲器,利用2 片SRAM(記為SRAM1 ,SRAM2) 存放采集到的圖像數據。

DSP 每執行一次復位,都將DROM 清零,在系統中沒有改變該比特位的設置, 這樣使得數據存儲空間的低48 k 字全都對應外部存儲器,其中低32 k 字空間映射為外掛FLASH ,用來存放引導程序、中斷矢量表和用戶代碼等內容,其他16 k 字的空間映射為SRAM(記為SRAM3)用來存放數據處理的結果。

對于擴展程序存儲空間、擴展數據存儲空間所需要的時延可以通過軟件編程的方法對DSP 的等待狀態寄存器(SWWSR) 進行設置,使之達到最快速度。這樣就避免了使用硬件進行握手通信,簡化了接口的設計。

程序存儲器的擴展

系統中實際采集到的圖像數據量大約有1 M ×8 b ,而VC5402 的數據空間只有64 k 字,并且VC5402 內部具有16 k 字的隨機存儲器和4 k 字的只讀存儲器,遠遠不能滿足存儲要求,因此需要將數據空間擴展到1 MB才能實現圖像數據的存儲。由于VC5402 的程序空間可以擴展到1 M ×16 b ,而且具有專門訪問擴展存儲器的指令。考慮到數據空間擴展的復雜性,我們將采集到的圖像數據直接存放在擴展的程序空間中。系統中選用兩片SRAM( IS61LV5128AL–12) 用來存放原始數據,IS61LV5128AL–12 芯片是512 k ×8 b 的高速CMOS 靜態存儲器,存取速度為12 ns。

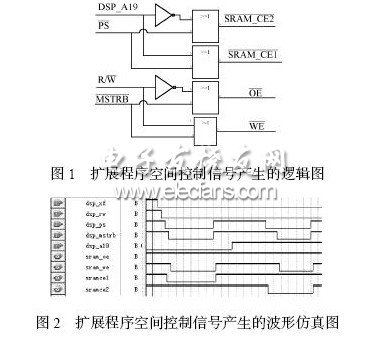

兩片存儲器接口的實現方案設計如圖1 所示.其中SRAM-CE1 ,SRAM-CE2 ,OE ,WE分別為2 片SRAM 的片選信號、讀使能信號、寫使能信號,這些邏輯組合是通過CPLD 實現的。仿真波形圖如圖2 所示。

進行程序空間擴展時,DSP 地址線的A (0) ~A (19)位都是有效的。VC5402 的程序空間被組織為16 頁,每頁64 k 字。內部64 k 字的程序空間可以直接訪問,當訪問超過64 k 字的程序區時,DSP 并不能提供直接訪問XPC寄存器的指令(程序空間是按頁進行管理的,頁地址放在XPC 寄存器中) ,這時使用WRITA 和READA 這兩條指令可以對高端程序空間進行訪問,要么把數據空間的數據送到程序空間,要么把程序空間的數據送到數據空間,采用累加器尋址方案才能影響XPC 寄存器的值。

這種方案的優點在于:不用進行數據區的擴展,直接利用VC5402 可擴展的程序區,簡單方便。

數據存儲器空間的擴展

脫機運行是此系統最主要的特點,所以必須考慮到存放脫機程序這一問題。在采集處理系統中,將存放程序的FLASH 映射在VC5402 的數據空間,由于圖像處理算法的復雜性,只靠VC5402 的數據空間難以滿足需求,因此需要對VC5402 進行數據空間擴展。

系統中選用了FLASH 存儲器SST39VF400A ,該芯片的容量是256 k ×16 b ,他是一種低電源電壓芯片,工作電壓為3. 3 V ,速度是70 ns ,能和VC5402 實現無縫接口,數據保存時間超過100 年,他具有容量大、掉電后數據不丟失、可在線快速讀寫、可整片或者分頁擦除等特點,同時由于其內部已經固化了相應的程序,使用時只需向特定的地址寫入特定的命令字序列,這樣使得SST39VF400A 的讀寫操作非常簡單靈活。

另外,擴展了64 k ×16 b 的SRAM( SRAM3 ,型號為CY7C1021) 用來存放數據處理的結果,映射到VC5402 的外部數據空間。CY7C1021 除了電源和地以外,還有幾個關鍵信號引腳如CE # ,WE # ,OE # ,BL E ,BHE 等。BL E決定該芯片的低字節是否有效,即數據位的低8 位是否有效,而BHE 則決定芯片的高字節(高8 位) 是否有效,引腳為低電平時有效。因為VC5402 的數據線為16 位,即其所用的寄存器和存儲器都應該是16 位, 所以應該將CY7C1021 的高低字節都使能,使其有效,將BHE ,BL E 通過360 Ω的電阻接地。

VC5402 的真正I/ O 引腳只有2 個BIO # 和XF ,而且是單向的,這樣他的I/ O 引腳太少,滿足不了設計的要求。本方案將VC5402 的數據總線D[ 0 :2 ]擴展為通用I/ O 口來彌補I/ O 口的不足。數據空間擴展的具體方法: 將CPLD 作為DSP 的1 個I/ O 口,DSP 的數據線D[ 0 :2 ] 接至CPLD 的輸入端。當DSP 的I/ O 選通信號IOSTRB #和IS # 有效時, DSP 通過這個I/ O 向CPLD 寫數據D[ 0 :2 ] ,在CPLD 內部進行邏輯組合,完成數據鎖存,等到數據選通信號有效時,將鎖存的數據輸出,產生分頁信號Page[ 0 :2 ] ,分別接在FLASH 和SRAM3 的高端地址上。

要訪問擴展的數據空間,必須通過CPLD 產生的頁信號進行選擇。256 k ×16 b 的FLASH 被組織為8 頁,每頁為32 k字長,信號Page2 , Page1 , Page0 負責對FLASH 各頁進行選擇。64 k ×16 b 的SRAM3 被劃分為4 頁,每頁為16 k字長,信號Page1 , Page0 負責對各頁進行選擇。在Flash中,每頁的32 k 字被映射到數據空間的08000 H ~0FFFFH 區域;在SRAM3 中,每頁的16 k 字被映射到數據空間的04000 H~07FFFH。頁信號產生的程序如下:

CPLD-CS < = DSP-IS OR (NOT DSP -A7) ;

CPLD-CS-IO < = CPLD-CS OR DSP-RW

OR DSP-IOSTRB ;

CPLD-CS-M < = DSP-DS OR DSP-MSTRB

OR DSP-RW;

PROCESS(CPLD-CS-IO ,CPLD-CS-M)

BEGIN

IF CPLD-CS-IO =′0′THEN

QQ < = DSP-D ;

END IF ;

IF CPLD-CS-M =′0′THEN

Q < = QQ ;

END IF ;

END PROCESS ;

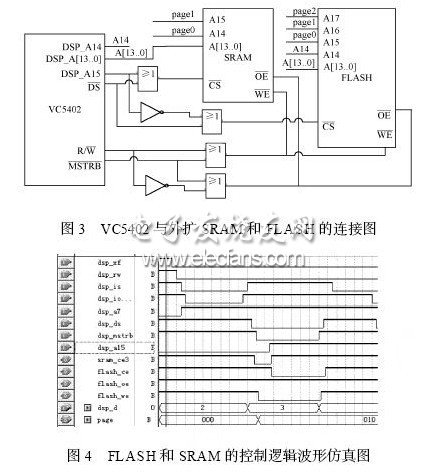

認真分析了本方案中VC5402 數據存儲空間的分配特點后,使用VC5402 的DSP A15 和數據選通信號DS #的邏輯組合來選通FLASH 和SRAM3 ,具體的連接如圖3所示,其轉換邏輯由CPLD 編程實現。

外擴FLASH 和SRAM 的讀寫控制信號的邏輯也是在CPLD 中實現的,數據存儲器擴展所需控制信號的仿真波形圖如圖4 所示。

對FLASH 空間的某一地址進行訪問時,應分為以下幾步:

首先,解析該地址,進行地址分割,低15 位為頁內地址,高3 位作為頁選擇地址;

其次,把頁選擇地址用PORTW 命令送到所分配的I/ O空間PA 中,等選通信號使能后,頁地址就在所選存儲器的高端地址線上;

最后,使用訪問數據的指令。由于VC5402 的數據是16 位的,因此在調用數據指令時,需要16 位的數據。這里,低15 位來自所要訪問的地址的低15 位,最高位補零。

要對Flash 存儲器的高端進行訪問,必須先對CPLD送數。如要尋址70000 H 存儲單元時,假定AR3 輔助寄存器指向某一存儲單元,CPLD 映射在VC5402 I/ O 空間的地址為PA ,其大致操作如下:

ST # 07H , *AR3

PORTW * AR3 ,PA

這樣,CPLD 充當的鎖存器將111 這3 位數給鎖存住,在選通FLASH 時,將數據111 送至FLASH 的A15~A17端,然后再對DSP 存儲器的地址0000 H 進行讀寫操作即可。

DSP 的擴展I/ O 端口

VC5402 僅有這2 個通用I/ O 引腳往往是不夠的,DSP 為了一些特殊的需要提供了多個片上設備,比如3 個多功能串口、HPI 接口等。這些片上設備在系統中并沒有用上,因此可以利用DSP 的擴展功能將這些設備的管腳擴展為通用I/ O 端口供系統使用。比如將HPI 端口的8 位并行數據線擴展為8 位I/ O 端口,用來和CPLD 進行通信,這些I/ O 口的擴展是通過對DSP 的相關寄存器進行相應的設置來實現的。

為了實現DSP 和CPLD 之間的交互,將HPI 的數據線用作通用I/ O 端口實現了VC5402 I/ O 口的擴展。HPI數據線擴展為通用I/ O 口的具體方法:在HPI 接口不允許,即在復位時HPIENA 引腳為低電平的情況下,使用2 個存儲器映射寄存器(通用I/ O 控制寄存器GPIOCR 和通用I/ O 狀態寄存器GPIOSR) 來控制HPI 數據引腳的輸入輸出。GPIOCR 和GPIOSR 在DSP 的物理地址分別是003CH 和003DH。

如要從擴展的HPI 口輸出數據40 H ,需要進行以下3 步操作:

第一步:在復位時,將HPIENA 引腳置為低電平;

第二步:將通用I/ O 控制寄存器GPIOCR 的值設置為0x00FF ;

第三步:將通用I/ O 狀態寄存器GPIOSR 的相應位設置為01000000 ,即40 H。

實現的程序代碼如下:

STM # 0x003C ,AR3 ; 選中控制寄存器

ST # 0x00FF , *AR3 ; 將HPI數據端置為輸出狀態

STM # 0x003D ,AR3 ; 選中狀態寄存器

ST # 0x0040 , *AR3 ; 輸出數據40H

結 語

利用CPLD 實現VC5402 的存儲器空間擴展,大大簡化了硬件電路的設計,編程靈活;調試時,只需對CPLD 電路進行調試,簡單方便,此方案可以推廣到其他便攜式圖像采集處理系統的存儲器擴展中。